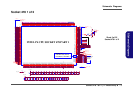

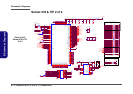

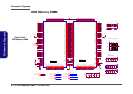

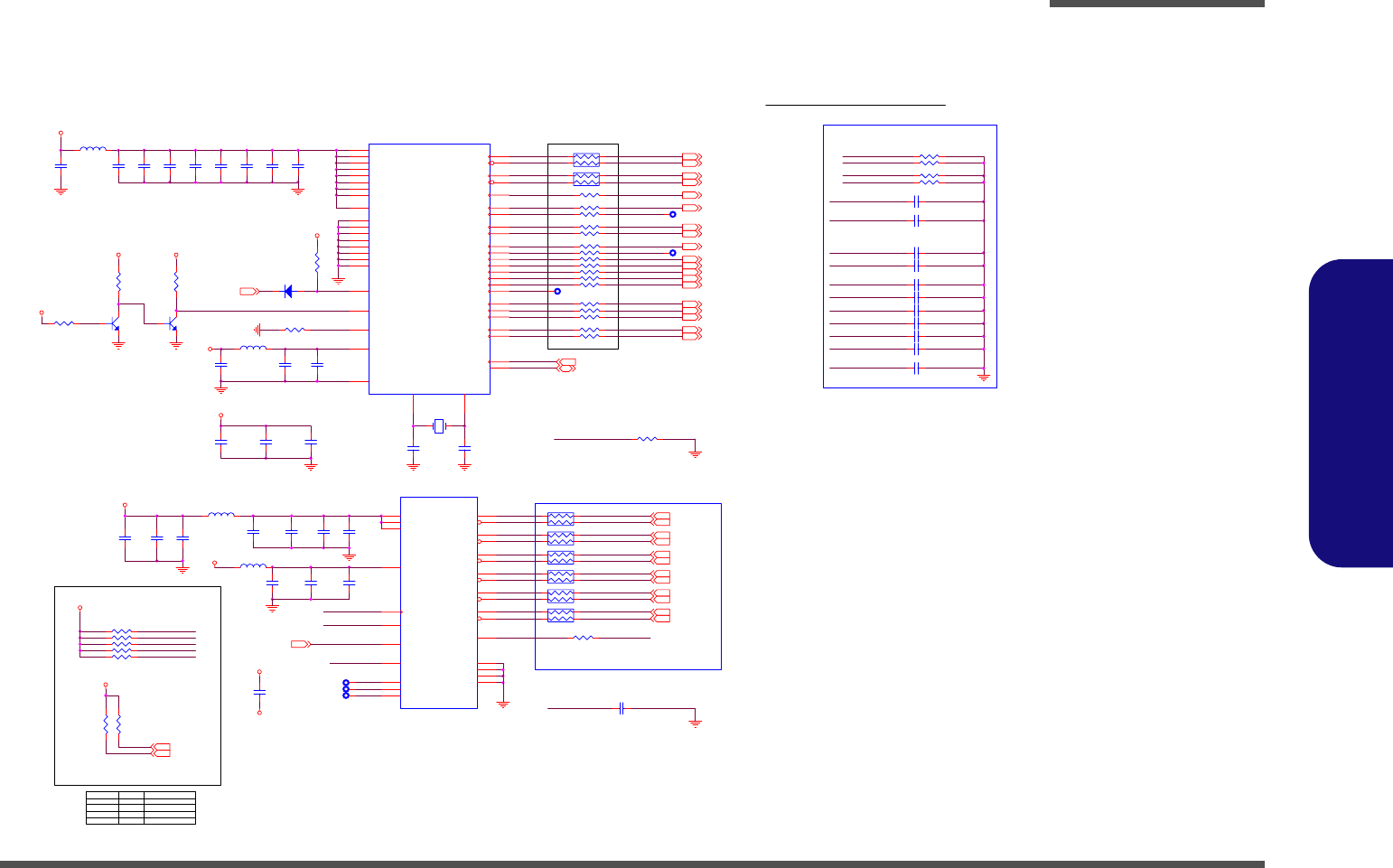

Schematic Diagrams

Clock Generator (71-D4000-D04) B - 5

B.Schematic Diagrams

Clock Generator

Sheet 4 of 35

Clock Generator

VTT

+2.5VS

+3VS

+3VS+3VS

+3VS

+3VS

+2.5VS

+3VS

+3VS

+3VS

+2.5V

+1.8VS

AGPCLK [5]

HCLK-650 [5]

ZCLK0 [9]

REFCLK1 [15]

PCICLKPCM [19]

HCLK-CPU# [3]

SDCLK [6]

HCLK-CPU [3]

CLKAPIC [15]

REFCLK0 [9]

HCLK-650# [5]

ZCLK1 [13]

PCICLKIO [22]

FWDSDCLKO[6]

PCICLK961 [13]

PCICLKH8 [24]

PCICLKLAN [25]

BSEL0 [3]

BSEL1 [3]

SMBCLK [7,15,24]

SMBDAT [7,15,24]

CPUSTP#[15,29]

SIO48M [22]

UCLK48M [16]

PCLK_80P [20]

DDRCLK3[7]

DDRCLK5[7]

DDRCLK#3[7]

DDRCLK#5[7]

DDRCLK0[7]

DDRCLK#0[7]

DDRCLK#2[7]

DDRCLK2[7]

DDRCLK4[7]

DDRCLK#4[7]

DDRCLK1[7]

DDRCLK#1[7]

HCLK-CPU

HCLK-CPU#

HCLK-650

HCLK-650#

SDCLK

AGPCLK

ZCLK0

UCLK48M

FB_IN

FS3

FS2

FS0

FS1

MULTISEL

FS4

DDRCLK3

DDRCLK5

DDRCLK#3

DDRCLK#5

FB_IN

BUF_2.5VS

FB_OUT

FB_IN

BUFFERVCC

FWDSDCLKO

SMBCLK

SMBDAT

REFCLK0

REFCLK1

CLKAPIC

HCLK-CPU

HCLK-CPU#

HCLK-650

HCLK-650#

AGPCLK

GCLK_AGP

ZCLK0

ZCLK1

PCICLK961

PCICLK1394

PCICLKH8

SDCLK

PCICLKIO

PCICLKLAN

PCICLK961

PCICLK1394

PCICLKPCM

PCICLKH8

PCICLKIO

PCICLKLAN

ZCLK1

FS0

FS1

AGP-1

SMBDAT

CPU-3

SD-1

CPU-2

CPU-4

FS2

FS3

AGP-2

MULTISEL

FS4

SMBCLK

CLK_VCC3

PCI-4

USB-1

PCI-2

CPU-1

PCI-3

ZIP-1

ZIP-2

PCICLKPCMPCI-1

UCLK48M

SIO48M

PCI-5

PCI-6

PCLK_80P

DDRCLK0

DDRCLK#0

DDRCLK#2

DDRCLK2

DDRCLK4

DDRCLK#4

DDRCLK1

DDRCLK#1

L21

FCM1608K121

1 2

L33

FCM2012V121

1 2

L94

FCM1608K121

1 2

L84

FCM2012V121

1 2

C76

0.1UF

C91

10PF

C92

10PF

C532

0.1UF

C121 10PF(R)

C86

0.1UF

C78

0.01UF

C74

10PF(R)

C119

10PF(R)

C77

10UF/10V

C533 10PF(R)

C207

0.1UF

C550

0.1UF

C75

10PF(R)

C557

0.1UF

C565

0.01UF

C90

0.1UF

C549

0.01UF

C105

0.1UF

C401

10UF/10V

C556

0.1UF

C118 10PF(R)

C115 10PF(R)

C114

10PF(R)

C73 10PF(R)

C102

0.1UF

C81

0.1UF

C84

0.1UF

C85

0.1UF

C104

0.1UF

C103

0.1UF

C83

0.1UF

R62

10K

R43

10K

R60 4.7K(R)

R334 22

R309 22

R335 22

R310

22

R311 22

R337 33

R384

22

R33

49.9_1%

R336

33

R34

49.9_1%

R44

0(R)

R35

49.9_1%

R36

49.9_1%

R341 33

R340 33

R296

4.7K

R283

4.7K

Q20

2N3904

B

E

C

R67 4.7K

R66 4.7K

R65 4.7K(R)

R61 4.7K(R)

RP44

4P2R-33

1

2 3

4

RP43

4P2R-33

1

2 3

4

RP60 4P2R-0

1

2 3

4

R59

10K

C120 10PF(R)

C117 10PF(R)

R331

33

Q19

2N3904

B

E

C

R332 33

R312

22

C82

0.01UF

R339 33

R333 33

Y5

14.318MHz

1 2

R338 33

U28

CLOCK GEN (650)

1

3

2

6

7

14

16

17

20

21

22

30

31

27

26

34

35

44

40

36

37

47

39

43

23

4

9

10

15

38

5

8

18

24

25

32

41

11

13

19

28

29

42

48

46

12

45

33

VDDREF

REF1/FS1

REF0/FS0

XIN

XOUT

PCICLK_F0/FS3

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

AGPCLK1

AGPCLK0

48M

24_48M/MULTISEL

SDATA

SCLK

CPUCLK1

CPUCLK0

VDDA

VSSA

SDCLK

CPUCLK#0

CPUCLK#1

PCICLK5

REF2/FS2

ZCLK0

ZCLK1

PCICLK_F1/FS4

IREF

VSSREF

VSSZ

VSSPCI

VSSPCI

VSS48

VSSAGP

VSSCPU

VDDZ

VDDPCI

VDDPCI

VDD48

VDDAGP

VDDCPU

VDDSD

VSSSD

PCI_STOP#

CPU_STOP#

PD#/VTT_PWRGD

R37

10K

D10

1SS355

AC

R313

22

R45

475_1%

C116 10PF(R)

R342 33

T

T

T

RP75 4P2R-0

1

23

4

T

T

RP76 4P2R-01

23

4

RP62 4P2R-01

2 3

4

U29

CLOCK BUFFER (DDR48)

22

8

9

20

18

6

11

15

28

19

21

1

5

14

16

25

27

2

4

13

17

24

26

3

12

7

23

10

SDATA

CLK_IN

NC

FB_IN

NC

GND

GND

GND

GND

FB_OUT

NC

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

VDD

VDD

SCLK

VDD

AVDD

RP61 4P2R-0

1

2 3

4

T

C208

10U(0805)

C560

10U(0805)

C523

10U(0805)

RP77 4P2R-0

1

2 3

4

C684

0.1UF

Main Clock Generator

By-Pass Capacitors

Place near to the Clock

Outputs

Clock Outputs

Damping Resistors

Place near to the

Clock Buffer (DDR)

By-Pass Capacitors

Place near to the Clock Buffer

Frequency

Selection

L L

H L

BSEL1 BSEL0 Function

H H

L H

ICS 93722

CY 28342

ICS 952001

14.381MHZ

48 MHZ

NEAR DDR SODIMM

PLEASE PLACE IN COMP SIDE

AND NEAR TOGETHER

FS4 FS3 FS2 FS1 FS0

0 0 0 1 1

CPU SDRAM ZCLK AGP PCI

100M 133M 66M 66M 33M

0 0 0 0 1 100M 100M 66M 66M 33M

CY28352