Schematic Diagrams

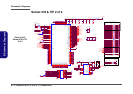

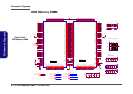

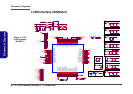

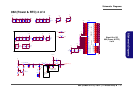

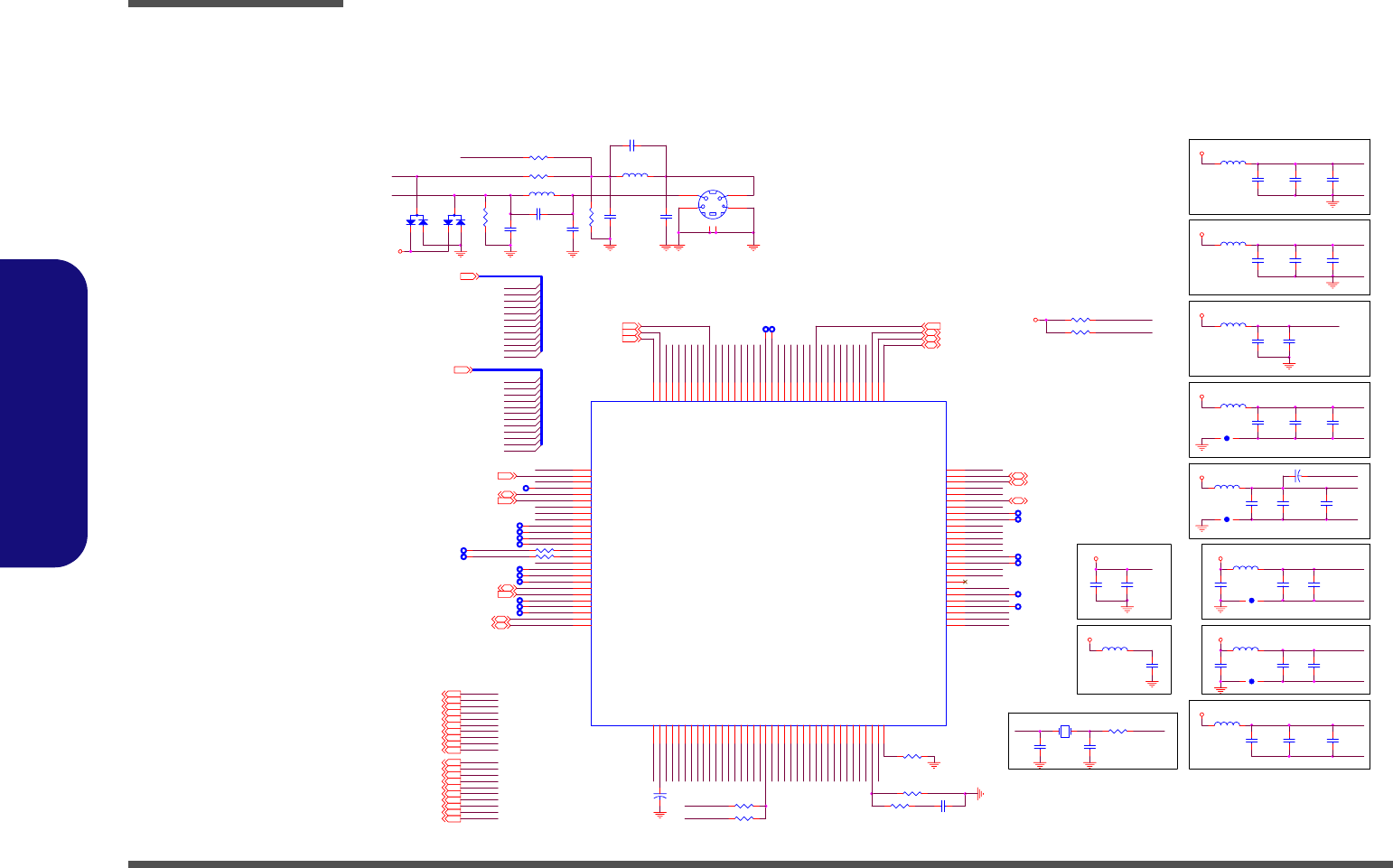

B - 12 LVDS Interface (SiS302LV) (71-D4000-D04)

B.Schematic Diagrams

LVDS Interface (SiS302LV)

Sheet 11 of 35

LVDS interface

(Sis302LV)

+5VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

VBGCLK [5]

PCIRST#[9,13,14,20,22,24]

VBHCLK[5]

VBCAD[5]

VAD[0..11][5]

VBD[0..11][5]

VAGCLK[5]

VAHSYNC[5]

VAVSYNC[5]

VADE[5]

VBCLK [5]

VBHSYNC [5]

VBVSYNC [5]

VBDE [5]

VBCTL0 [5]

VBCTL1 [5]

INTA#[9,13]

ENAVDD[11]

ENABKL[11]

LL1C+[11]

LL1C-[11]

LDC2+[11]

LDC2-[11]

LDC1+[11]

LDC1-[11]

LDC0+[11]

LDC0-[11]

LL2C+[11]

LDC5+[11]

LDC6-[11]

LL2C-[11]

LDC5-[11]

LDC6+[11]

LDC4+[11]

LDC4-[11]

LDC3+[11]

LDC3-[11]

LDC7-[11]

LDC7+[11]

V2COMP

LPLLVDD

LDDCDATA

LDDCCLK

LL2C+

LL2C-

LDC6+

LDC6-

LDC5+

LDC5-

LDC4+

LDC4-

COMPOSITE Z1301

VBRCLK

LDDCDATA

LDDCCLK

LVDD1

VBD11

VBD6

TVPLLVDD

DAC_GND

V2COMP

LDC0-

LDC3+

LPLLVDD

LGND

ENAVDD

VBHCLK

VAVSYNC

DGND

DAC_GND

LDC2+

DVDD

DGND

VBRCLK

TVPLLGND

DAC_VDD

LDC3-

LL2C-

VREF2

VAD8

VAD3

VAD1

VBD0

LVDD2

LGND

TVPLLVDD

LVDD2

DVDD

VBD1

LGND

VAGCLK

VAD5

DGND

VBOSCO

LDC2-

DVDD

DGND

VAD9

VAD6

VAD0

VBD2

VBCLK

COMPOSITE

VBOSCO

LVDD1

DAC_GND

TVPLLGND

C

DGND

DVDD

DVDD

VBD10

VBD9

VBD3

IOCS

VBGCLK

DAC_VDD

VAD11

LDC6+

DAC_VDD

LVDD2

LVDD2

LPLLCAP

V5V

DGND

DGND

DVDD

LDC4-

LVDD1

LDC7+

VREF2

VAD7

DVDD

C

LDC4+

LDC5-

LL2C+

VDDV

ENABKL

VAD10

VAD4

VBD8

VBD5

Y

LGND

LGND

LDC7-

LVDD1

PCIRST#

VADE

DVDD

VBD4

VSWING

LL1C+

LPLLGND

Y

V5V

INTA#

ISET

LL1C-

LGND

DGND

VAD2

VBDE

VBCTL1

VDDV

LDC0+

LDC5+

LGND

LPLLVDD

VAHSYNC

DGND

VBD7

LGND

LDC6-

VBD[0..11]

VBD8

VBD5

VBD9

VBD6

VBD3

VBD0

VBD11

VBD7

VBD4

VBD10

VBD1

VBD2

VAD[0..11]

VAD0

VAD10

VAD3

VAD11

VAD8

VAD6

VAD9

VAD2

VAD7

VAD4

VAD5

VAD1

VBVSYNC

VBHSYNC

VBCAD

VBCTL0

LDC1-

LDC1+

LDC0-

LDC2+

LDC2-

LL1C+

LL1C-

LDC0+

LDC1+

LDC1-

LDC3+

LDC3-

LDC7+

LDC7-

LPLLGND

L11

FCM1608K121

L12

FCM1608K121

L13

FCM1608K121

L14

FCM1608K121

L19

FCM1608K121

L20

FCM1608K121

C42

NC/0.1uF

L18

FCM1608K121

R23

NC

R268 6K

R269 2K

C49

NC

R20 100

R19 100

L17

FCM1608K121

R202

75

C261

330PF

D22

DA204U(R)

C

A

AC

C250 33PF(R)

C262

330PF

R212 0

C251

330PF

R213

75

R211 0(R)

D23

DA204U(R)

C

A

AC

L47

2.7UH

1 2

C249

330PF

L46

FCM1608K-121T07

1 2

C248 33PF(R)

Y3

14.318MHZ

R24 10

L15

FCM1608K121

N5

N3

N2

N4

R242 2.2K

R241 2.2K

R22 0

U22

SIS302LV

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

77

74

75

76

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

LVDSPLLVDD/LPLL

RESERVED/LPLLCA

LVDSPLLVSS/LPLL

LAVSS/LGND

RESERVED/LL2C

RESERVED/LL2C*

LAVDD/LVDD

RESERVED/LDC7

RESERVED?LDC7*

LAVSS/LGND

RESERVED/LDC6

RESERVED/LDC6*

LAVDD/LVDD

RESERVED/LDC5

RESERVED/LDC5*

LVDSPLLVSS/LGND

RESERVED/LDC4

RESERVED/LDC4*

LVDSPLLVDD/LVDD

LAVDD/LVDD

LX3P/LDC3

LX3N/LDC3*

LAVSS/LGND

LXC1P/LL1C

LXC1N/LL1C*

LAVDD/LVDD

LX2P/LDC2

LX2N/LDC2*

LAVSS/LGND

LX1P/LDC1

LX1N/LDC1*

LAVDD/LVDD

LX0P/LDC0

LX0N/LDC0*

LAVSS/LGND

EXTSWING/VSWING

DACVDD/DACVDD

V2RSET/ISET

DAC_GND/DAC_GND

V2COMP/DACB0

IOCOMP/DACA0

RESERVED/DACB1

IOY/DACA1

RESERVED/DACB2

IOC/DACA2

RESERVED/DACB3

DAC_VDD/DACA3

DAC_GND/DAC_GND

IOCS/C/HSYNC

RESERVED/BOC/VS

PLL1GND/TVPLL_G

VBRCLK(XIN)/XIN

VBOSCO/XO

PLL1VDD/TVPLL_V

DVDD0/TVPLL_VDD

TSCLKI/GPIO4

TVCLKO/GPIO[5]

DVSS0/RESET*

VBCLK/P-OUT

OVDD/VDDV

DVSS1/VREF1

VBCTL1/FLD/STL1

VBDE/DE1

DVDD1/DVDD

V1/VBVSYNC

H1/VBHSYNC

DGND/VBCTL0

D1[0]/VBD0

D1[1]/VBD1

D1[2]/VBD2

D1[3]/VBD3

D1[4]/VBD4

D1[5]/VBD5

D1[6]/VBD6

XCLK1*/DVDD2

DGND/DVSS2

XCLK1/VBGCLK

D1[7]/VBD7

D1[8]/VBD8

D1[9]/VBD9

D1[10]/VBD10

D1[11]/VBD11

DVDD/RESERVED

DVDD/RESERVED

D2[0]/VAD0

D2[1]/VAD1

D2[2]/VAD2

D2[3]/VAD3

D2[4]/VAD4

D2[5]/VAD5

XCLK2*/DVDD3

DGND/DVSS3

XCLK2/VAGCLK

D2[6]/VAD6

D2[7]/VAD7

D2[8]/VAD8

D2[9]/VAD9

D2[10]/VAD10

D2[11]/VAD11

DGND/OVSS

H2/VAHSYNC

V2/VAVSYNC

DVDD/DVDD4

DE2/VADE

FLD/STL2/DVSS4

AS/RESERVED

SPD/VBCAD

SPC/VBHCLK

HIN/DVSS5

VIN/DVDD5

VREF2/OVDD

SDD/GPIOA(GPI)

SDC/GPIOB(GPI)

DD1/GPIOC(GPI)

DC1/GPIOD(GPI)

DD2/LDDCDATA

DC2/LDDCCLK

V5V/V5V

HOUT/V2HSYNC

VOUT/V2VSYNC

HPD/LCDSENSE

HPINT*/INTA#

GPIO[0]/EXTRSTN

GPIO[1]/PFTEST1

GPIO[2]/PFTEST2

GPIO[3]/PFTESTO

ENAVDD/GPIOG(GP

ENABKL/GPIOH(GP

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

R267 147

C36

0.1UF

C35

0.1UF

C39

0.1UF

C40

0.1UF

C59

0.1UF

C66

0.1UF

C68

0.1UF

C41

0.1UF

C51

0.1UF

C34

0.1UF

C57

0.1UF

C56

0.1UF

C55

0.1UF

C46

0.1UF

C47

0.1UF

C321 1UF

C32

0.1UF

C69

0.1UF

C37

10UF/10V

C38

10UF/10V

C60

10UF/10V

C67

10UF/10V

C50

10UF/10V

C33

10UF/10V

C58

10UF/10V

C65

10UF/10V

C48

10UF/10V

C52

22P

C43

22P

JTV1

SVIDEO CON

1

34

2

5

6

T

T

301LV/302LV:R894/R895

PIN(GND1,GND2)=GND

Spread range:R120:+-1.5%/+-2.5%

Choose clock source:main board/crystal

R1 :NC/22