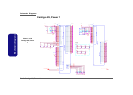

Schematic Diagrams

Penryn 1/2 B - 3

B.Schematic Diagrams

Penryn 1/2

Layout Note:

H_DSTBN#14

H_A#16

R 373 * 10m il_s hor t

CPU_BSEL118

H_D STBP #14

H_D#59

H_D#61

H_D#7

H_A#28

R391 *10K_04

1.05VS

H_D#44

H_D#29

H_RE Q#2

H_BPRI# 4

H_D#16

H_PR DY#

H_D#19

R358 56_04

3.3VS3,5,9,12,13,14,15,16,19,20,21,22,23,24,25,26,28,30,32,33,35,36,37,38

H_HITM# 4

H_D#52

H_A#24

H_FERR#13

H_ADSTB#04

H_D#8

H_A#5

Layout note:

H_TMS

R380

2K _1% _0 4

H_BPM0#

H_D#26

H_D#28

R387 4.7K_04

H_ADSTB#14

Z0211

VDD313,19,22,24,29,32,33,34,37

H_PR OCH OT#

H_D#49

PVT

H_BNR # 4

H_A#[35:3]4

H_RS#1 4

COMP1

R390 *0_04

H_INTR13

CPU_TEST4

R52 54.9_1%_04

1.05VS

H_D#0

H_DS TBP#2 4

H_D#32

H_A#30

H_TDI

H_IER R#

H_TRST#

V_THRM

VDD3

H_TRDY # 4

H_THER MD C1

H_D#56

H_A#19

CPU_BSEL218

R392

*10K_1%_04

R56

54 . 9_1% _04

H_A#22

CLK_CPU_BC LK# 18

H_A#35

H_TDO

PM_THRM# 3,15,22

H_D#37

R376 *1K_04

H _TH ERMDC23

H_D#15

H_A#23

R329 54.9_1%_04

H_D#22

H_A#10

U24

ASC7525

1

2

3

4

5

6

7

8

VDD

D+

D-

TH ERM

GND

ALERT

SDATA

SCLK

CO MP3

PVT

1.05VS3,4,5,9,13,16,18,33

H_THERMDC1

CO MP0

CPU_TEST2

H_D#[63:0] 4

Z0213

H _R EQ#[4:0]4

H_D#13

H_D#46

R641 54.9_1%_04

R375 *1K_04

H_BPM_2#1

H_TH ERMDA23

H_D#39

H_A#29

ADDR

GROUP_0

ADDR

GROUP_1

CONTROL

XD P/I TP SIGN ALS

H CLK

THERMA L

RESE RVE D

ICH

U22A

SOC KET G 479P

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RSVD[01]/BPM_2#[1]

RSVD[02]/BPM_2#[0]

RSVD[03]/THRMD A_2

RSVD [04]/THR MD C_2

RSVD[05]BPM_2#[2]

RSVD[06]

RSVD[07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

ADSTB[0]#

ADSTB[1]#

RSVD [08]/TDO _M

BCLK[0]

BCLK[1]

BNR#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

BPRI#

BR0#

DBR #

DBSY#

DEFER #

DRDY#

FERR#

HIT#

HITM#

IERR #

IGNNE#

INIT#

LIN T0

LIN T1

LOCK#

PRDY #

PREQ#

PROCH OT#

REQ [0]#

REQ [1]#

REQ [2]#

REQ [3]#

REQ [4]#

RESET#

RS[0]#

RS[1]#

RS[2]#

SMI#

STP CLK#

TCK

TDI

TDO

THERMTRIP#

THERMDA

TH ERM DC

TMS

TRDY #

TRST#

A[32]#

A[33]#

A[34]#

A[35]#

RSVD [09]/TDI_M

If PROCHOT# is not ured,then it must be

terminated with 56-Ohm pull-up to VCCP.

H_RS#2 4

H_D#4

CPU_GTLREF1

H_TDI

H_A#13

H_A#12

Layout note:

Zo=55 ohm, 0.5"max

for GTLREF

H_A#25

R382

54.9_1%_04

H_D#42

H_A#20

H_D#17

H_D#62

H_D#2

H_D#23

H_BPM_2#0

H_PR OCH OT#

H_D#34

DVT

H_A#3

H_DINV#14

PSI# 35

H_RE Q#4

COMP3

H_D#5

H_IG NNE #13

H_THER MDA1

H_D#35

H_D#36

Near to Thermal IC

H_TMS

H_A#8

R326 54.9_1%_04

C463

10u_10V_08

H_DP SLP# 13

H_A#[35:3]4

H_TCK

H_DBSY # 4

R369 56_04

H_D#11

H_A#32

H_A20M#13

SMD_THERM1 3,22

H_THERMDA1

H_DINV#04

H_A#34

Layout Note:

H_D#43

H_INIT# 13

H_D#30

CPU_TEST1

H_A#7

H_BPM2#

H_TRST#

H_NMI13

H_D#14

H_ALERT1

G781-1 SMbus = 4Dh

V_THRM

H_DS TBN #2 4

H_RE Q#3

H_D#3

R355

100K_04

R381

27.4_1%_04

DVT

H_DSTBN#04

H_D#1

H_D#50

H_D#10

3.3VS

H_A#27

H_D#54

H_DS TBN #3 4

H_RS#0 4

H_D#63

H_D#55

R327 54.9_1%_04

10mils

CPU _TH ERM 22

H_D#58

H_D#20

H_D STBP #04

Z0206

ITP_DBRS T#

H_IER R#

H_PR EQ#

H_DEFER # 4

H_D#57

H_A#31

SMC_THERM1 3,22

H_DP WR# 4

C468 *0.1u_X7R_04

H_D#51

H_PR EQ#

H_D#9

H_A#9

H_D#60

H_RE Q#1

H_CP USLP# 4

H_ADS# 4

H_D#40

H_A#21

Z0212

H_A#33

H_A#15

VDD3

H_D#[63:0]4

R57

27.4_1%_04

H_D#[63:0]4

H_D#38

H_A#4

R389 *10mil_short

H_D#48

H_HIT# 4

TD I_M3

H_A#26

H_D#18

R379 1K_1%_04

H_DP RSTP# 5,13,35

V_THRM3

H_RE Q#0

H_A#14

H_D#25

Near toCPU

H_LOCK# 4

H_D#21

Layout Note:

VDD3

H_SMI #13

H_A#18

3.3V14,15,16,19,21,27,28,29,30,31,32,34,36,37,38

H_A#11

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

PM_THRM TRIP# 5,13

H_STPCLK#13

COMP2

H_DR DY# 4

H_PWR GD 13

TD O_ M3

H_D#27

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

H_D#31

Z0210

DA TA G R P 0

DA TA G R P 1

DATA GRP 2DATA GRP 3

MISC

U22B

SOC KET G 479P

R26

U26

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M2 4

L22

M2 3

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD24

G25

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

E25

AC22

AD23

AF22

AC23

E23

K24

G24

AF1

H25

N24

U22

AC20

E5

B5

D24

J26

L26

Y26

AE25

H26

M2 6

AA26

AF24

AD26

AE6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23

C3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

DINV[ 0]#

DINV[ 1]#

DIN V[2]#

DIN V[3]#

DPR STP#

DPSLP#

DPWR #

DSTBN[0]#

DSTBN[1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTLR EF

PSI#

PWR GOOD

SLP#

TEST3

BSEL[ 0]

BSEL[ 1]

BSEL[ 2]

TEST2

TEST4

TEST6

TEST1

TEST7

H_D#33

H_D#47

H_D#[63:0] 4

CPU_BSEL018

H_BR0# 4

H_CPU RST# 4

R383 4.7K_04

C478

1000p_50V_04

R357 1K_04

H_DI NV#2 4

ITP_DBRS T#

H_A#6

H_D#24

RT2

*NTC_100K_06

12

H_TCK

H_BPM3#

H_D#41

? ? ? VGA? ? thermal IC ? ? ? ?

CPU _GTLR EF23

H_D#6

CLK_CPU_BC LK 18

H_D#53

H_D#12

H_D#45

H_A#17

ADM1031 SMbus = 98h

3.3V

H_BPM_2#2

CO MP1

R388

*10K_04

H_DI NV#3 4

CO MP2

Within 2.0"

of the CPU

H_DS TBP#3 4

CPU_GTLREF2

H_BPM1#

COMP0

Sheet 2 of 42

Penryn 1/2