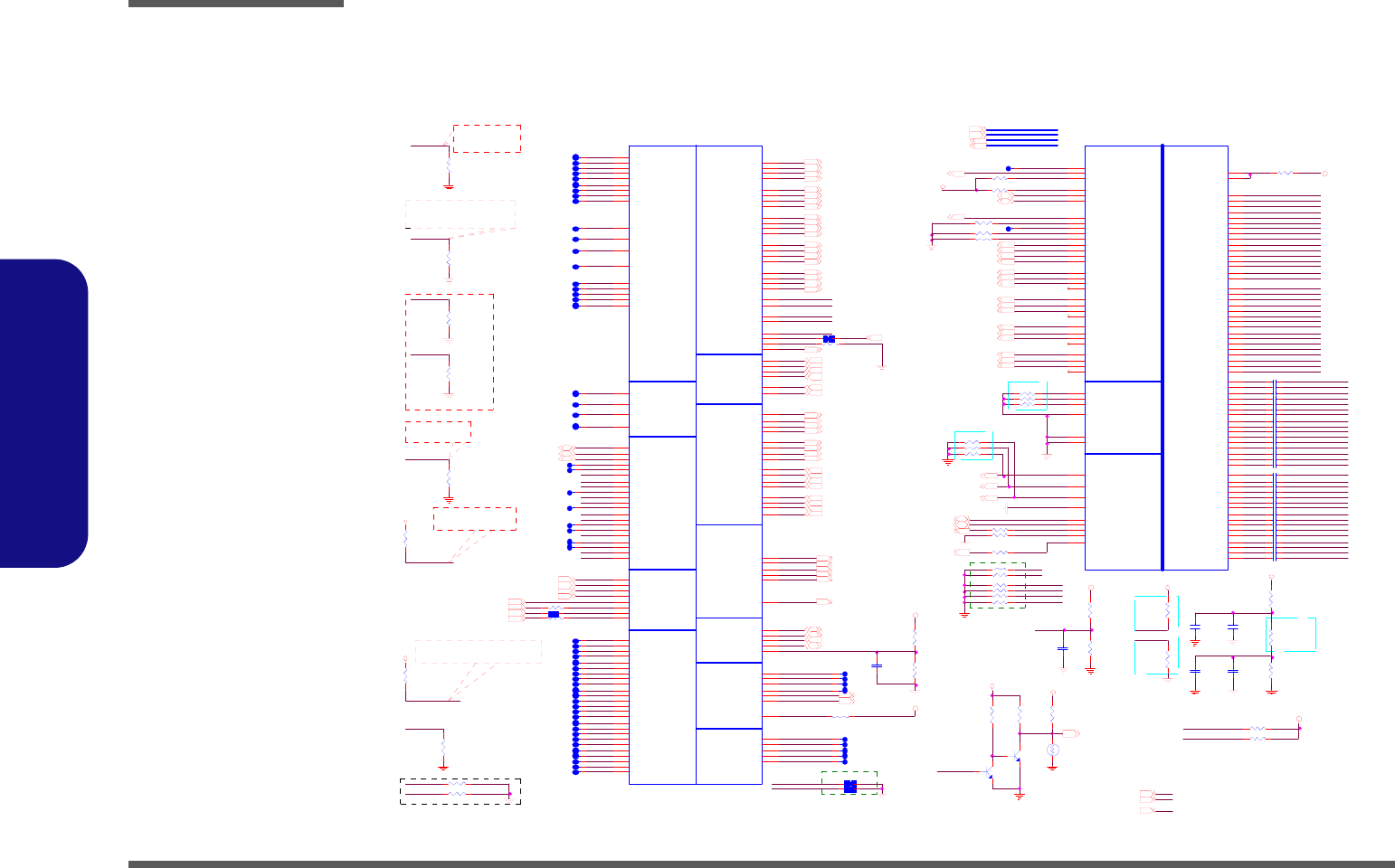

Schematic Diagrams

B - 6 Cantiga 2/6, PEG

B.Schematic Diagrams

Cantiga 2/6, PEG

Sheet 5 of 42

Cantiga 2/6, PEG

DMI_TXP3 14

H_DPRSTP#2,13,35

M_ VRE F_MCH

M_CLK_DDR 2 11

GM_DAC_B28

PEG_TXN8

R109 *10mil_short

3.3VS

PEG_TXP6

C155 0.1u_10V_04

R112 0_04

GTP5

PM_NC20

C165 0.1u_10V_04

CL_DATA0 15

M_ CK E1 1 0

PM_EXTTS0#

MCH_ CF G_ 1 0

R72

*1 K_04

ALLZ

DDPC _CT_DATA

PEG_TXN4

R81 0_04

MCH_ CF G_ 5

R128

49.9_1% _04

3.3VS

R119 0_04

DFGT_VID_330

PM_NC9

PEG_RXN7

R129

* 2. 21K_1% _04

CLK_DREF_SS# 18

GTP0

GM_LVDS_L1P

Z0505

Z05 69

C152 0.1u_10V_04

SDVO_CT_DATA

R163

1K_1%_04

C148 0.1u_10V_04

R82 *2.37K_1%_04

PCIe Graphics Lane

DMI Lne Reversal

1.05VS

CL_R ST#0 15

PEG_RXP5

PM_RSTIN#

Z0575

M_VR EF_ MCH

MCH_ CF G_ 1 6

PEG _RXN [0. .15]

C156 0.1u_10V_04

R78

*1 K_0 4

Q51

*2 N3 90 4

B

E C

M_ CS 1# 1 0

Z0507

PM_EXTTS1#

Low= XOR mode enabled

High=Disable(Default)

PM_NC1

GTP3

GM_LVDS_L2P

1.5V

PEG_TXP3

Z0562

Z0509

MCH_ CF G_ 1 6

MCH_ CF G_ 6

C168 0.1u_10V_04

R122

* 2. 21K_1% _04

C145 0.1u_10V_04

R147

1K_1%_04

DELAY _PWRGD15,35

M_CLK_DDR 0# 10

MCH_ CF G_ 9

R359 0_04

DMI_TXP2 14

MCH_ TSATN#

PEG_TXN5

C153 0.1u_10V_04

Z0511

Z0572

Z0582

Z0518

M_CLK_DDR 3# 11

PEG_RXP11

Z0517

C169 0.1u_10V_04

DMI_RXP1 14

DMI_TXP0 14

R114 0_04

GM_LVDS_UCLKN12

DMI_TXN0 14

MCH_ CL KREQ# 18

GM_LVDS_U0 P

L_CTRL_CLK

1.05VM

MC H_CFG_13

MCH_ CF G_ 4

GM_DAC_HSYNC28

PEG_RXP3

C146 0.1u_10V_04

R94 0_04

Low= disable

High=enable(Default) GTN11

PEG_COMP

MCH _CF G_9

GM_LVDS_U0P12

M_CLK_DDR 1 10

Z0535

C253

2.2u_6.3V_06

DMI_TXP1 14

GM_LVDS_LCLKN

Z0574

DDPC _CT_CLK

PM_NC12

GTP9

SM_RCOMP

GM_EDID _DATA

DFGT_VR_EN 30

PEG_RXN5

PEG_TXP12

C255

2.2u_6.3V_06

C141 0.1u_10V_04

R101 0_04

CLK_DREF# 18

GTP11

PM_NC14

PM_NC4

PM_NC19

PM_NC8

R79

*4.02K_1%_04

C144 0.1u_10V_04

Low=Interface is enable

High= disable(Default)

PM_NC16

GTN8

Z0583

C162 0.1u_10V_04

C143 0.1u_10V_04

FSB Dynamic ODT

GM_LVDS_L1N12

GTP15

MCH _CF G_19

C164 0.1u_10V_04

GTN3

SM_RCOMP_VOH

PEG_TXN14

PEG_RXP12

GM_LVDS_U1N12

PEG_RXP2

MCH_CLKREQ#

MPW ROK 1 5

1.5V_PWRG D 15,31

Z0514

MCH_ CF G_ 1 0

R146

511_1%_04

C254

2.2u_6.3V_06

GM_DAC_VSYNC28

ME_ J_TMS

CH

SM_RCOMP#

R85 0_04

M_CLK_DDR 1# 10

Z0576

GTP2

Z0510

GTP13

Z0585

PM_EXTTS1#

GTN1

ITPM Hos t Interface

CL_CLK0 15

GTP12

SDVO_CT_DATA

R113 0_04

R366

* 2. 21K_1% _04

MCH _CF G_12

CL_VREF

R77

10K_1%_04

SM_RCOMP_VOL

MCH_ CF G_ 1 4

SM_RCOMP_VOH

PEG_TXP9

R363 *2.21K_1%_06

1.5V

1.5V

3.3VS2,3,9,12,13,14,15,16,19,20,21,22,23,24,25,26,28,30,32,33,35,36,37,38

GM_LVDS_U2P12

Z05 67

Z05 71

GM_LVDS_L1N

PM _SYN C#15

PEG_TXN7

PEG_TXP1

SM_RCOMP#

C167 0.1u_10V_04

clock un-gating

Low= Reverse Lanes

High=Norm al

Operation(Default)

Low=Only(Default)

H igh=sim ul taneous ly

1.5V7,9,10,11,27,31,33

MCH_BSEL218

M_ CS 2# 1 1

M_ ODT 0 10

C210

0.1u_10V_04

M_CLK_DDR 2# 11 GM_EDID_DATA12

PM_NC25

CV

C147 0.1u_10V_04

GM_LVDS_L2N12

GM_LVDS_U2 P

PM_NC3

PEG_RXN1

PEG_RXN11

3.3VS

3.3VS

MCH_TSATN#

C166 0.1u_10V_04

C154 0.1u_10V_04

ME_ J_TC K

L ow= N orm al o pe ratio n(D e fa ul t)

High=Reverse Lanes

M_ CK E2 1 1

Z0502

PEG_RXN0

PEG_RXP14

C251

0.01u_50V_04

R160

80.6_1% _04

R162

3.01K_1% _04

PM _EXTTS0#10

GTN15

MCH_ CF G_ 8

R75 *30.1_1%_04

Digital Dispaly Po rt Concu rr ent wiht PCie

DMI_TXN1 14

M_CLK_DDR 0 10

DFGT_VID_130

PEG_RXN4

GM_BLON12

DMI_RXP0 14

GTN5

PEG_TXP4

M_ CK E0 1 0

MCH_ CF G_ 1 7

PEG_TXP2

SDVO_CT_CLK

R103 0_04

PM_NC17

PEG_TXN1

DMI_RXN2 14

CLK_DREF 18

PEG_RXN9

RT1

NTC_100K_06

12

PM_DPRSLPVR15,35

PM_NC18

PEG_RXP7

PEG_RXN8

GM_EDID _CLK

C174 0.1u_10V_04

C149 0.1u_10V_04

3.3VS

Z0504

GM_LVDS_U1P12

GM_LVDS_U2N12

PEG_TXN6

PM_NC2

PEG_TXN15

MCH_ CF G_ 7

R161

80.6_1% _04

C175 0.1u_10V_04

PEG_TXP13

MCH_ CF G_ 1 5

MCH _CF G_20

GM_LVDS_L2P12

MCH_ CF G_ 1 8

PEG_R XN[0..15]37

PEG_TXN[0..15]

Low= ALLZ mode enabled

High=Disable(Default)

GM _ENAVDD12

GM_LVDS_L0N12

SDVO_CT_CLK

GTP8

DFGT_VID_430

M_ ODT 3 11

PEG_TXN[0..15]37

GTN9

Z0515

PEG_TXN13

PEG_TXP15

GTN2

PEG_RXP[0..15]

DVT: For PM

PM_THRMTRIP#2,13

PM_NC22

PEG_RXN6

GTP7

PEG_RXN2

CH

R126 *10mil_short

R164

1K_1%_04

GTN0

GTP1

PEG_RXP1

PEG_RXN10

PEG_RXN13

R127 0_04

R80 *30.1_1%_04

GM_LVDS_LC LKP12

PEG_RXP8

MCH_ CF G_ 1 9 C160 0.1u_10V_04

C252

0.01u_50V_04

GM_DDC_DATA28

GM_LVDS_UCLKP12

ME_ J_TD I

PEG_TXP0

MCH _CF G_5

R105 0_04

DMI X2 select

GM_DAC_G28

M_ CS 0# 1 0

DMI_RXP2 14

M_ ODT 1 10

PEG_TXP7

GTN12

PM_NC10

PEG_TXN9

R156

10K_1% _04

DVT: For PM

GM_LVDS_LCLKP

R74 0_04

VCC_PEG

C151 0.1u_10V_04

M_CLK_DDR 3 11

PEG_TXP8

PM_NC6

R115 *10K_04

MCH_ CF G_ 2 0

L_CTRL_CLK

GTP14

PEG_RXN15

GM_LVDS_U1 P

R364

*2.21K_1%_04

R108 *10mil_short

CLK_PCIE_3GPLL# 18

PEG_RXP6

PM_NC23

GTN10

GM_LVDS_UC LKP

Z0573

C161 0.1u_10V_04

R157

10K_1% _04

Z0501

Z0561

Z0506

MCH_ CF G_ 7

DMI_RXN3 14

CLK_DREF_SS 18

GM_EDID_CLK12

DMI_TXN3 14

PEG_RXP0

1.05VS2,3,4,9,13,16,18,33

GM_LVDS_U0 N

PEG_RXP15

R368 56_04

Q21

*2 N3 90 4

B

E C

DFGT_VID_030

Z0508

MCH_ CF G_ 1 3

M_ CS 3# 1 1

DMI_RXN1 14

SM_RCOMP_VOL

PEG_TXP[0..15]37

MCH_ CF G_ 6

PEG_RXN3

GTN4

L_CTRL_DATA

LVDS

PCI-EXPRESS GRAPHICS

TV

VGA

U25C

CANTIGA

T37

T36

H44

J46

L44

L40

N41

P48

N44

T43

U43

Y43

Y48

Y36

AA43

AD37

AC47

AD39

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

J41

Y40

M4 0

M4 2

R48

N38

T40

U37

U40

M4 6

AA46

AA37

AA40

AD43

AC46

M4 7

J42

L46

M4 8

M3 9

M4 3

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

M32

M33

K33

J33

M29

C44

B43

E37

E38

C41

C40

H47

E46

G40

D45

F40

B37

A37

A41

H38

G37

G38

F37

G32

F25

H25

K25

H24

E28

H32

J32

G28

J29

E29

J28

G29

L29

H48

B42

L32

C31

E32

A40

B40

J37

K37

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_R X_0

PEG_R X_1

PEG_R X_2

PEG_R X_3

PEG_R X_4

PEG_R X_5

PEG_R X_6

PEG_R X_7

PEG_R X_8

PEG_R X_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_10

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_1

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX#_2

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

L_CTRL_CLK

L_CTRL_DATA

L_DDC _CLK

L_DDC _DATA

L_VDD_EN

LVD S_IBG

LVD S_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA_1

LVDSA_DATA_2

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA_1

LVDSB_DATA_2

L_BKLT_EN

TVA_DAC

TVB_DAC

TVC_DAC

TV_RTN

CRT_BLUE

CRT_D DC_CLK

CRT_D DC_DATA

CRT_G REEN

CRT_H SYNC

CRT_TVO_IREF

CRT_R ED

CRT_IRTN

CRT_VSYNC

LVDSA_DATA_0

LVDSB_DATA_0

L_BKLT_C TRL

TV_DCONSEL_0

TV_DCONSEL_1

LVDSA_DATA#_3

LVDSA_DATA_3

LVDSB_DATA#_3

LVDSB_DATA_3

R207 *10mil_short

For PM

SM_RCOMP

GM_LVDS_U0N12

GM_LVDS_L0N

R121 10K_04

PM _EXTTS1#11

L_CTRL_DATA

GM_LVDS_L0P

Z0534

MCH_ CF G_ 3

PEG_TXN0

PEG_RXP13

PEG_TXP14

GM_LVDS_L1P12

DMI_RXN0 14

CLK_PCIE_3GPLL 18

ME_ J_TD O

GTP6

PEG_RXP10

PLT_RST#14,22,37,38

PM_NC7

CV

Z0513

C173 0.1u_10V_04

PM

MISC

NC

DDR CLK/ CONTROL/COMPENSATIONCLK

DMI

CFG

RSVD

GRAPHICS VIDMEHDA

ME JTAG

U25B

CANTIGA

AP24

AT21

AV24

AR24

AR21

AU24

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BC36

BD17

AY17

BF15

AY13

BG22

BH21

P29

R28

P25

T25

R25

T28

P20

P24

C25

N24

M2 4

E21

C23

C24

N21

P21

T21

R20

M2 0

L21

H21

R29

N33

P32

AT4 0

AT1 1

B38

A38

E41

F41

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

AL 34

AN35

AK34

AM35

BG23

BF23

BH18

BF18

B7

AU20

AV20

AY21

AH 9

AH10

AH12

AH13

M3 6

N36

R33

T33

B33

B32

G33

F33

C34

BF28

BH28

T20

R32

K12

AH37

AH36

AN36

AJ35

AH34

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH 6

BH 5

BG 4

G36

E36

K36

T24

H36

B12

E43

F43

BH 3

E33

B31

N28

BF3

BH 2

BG 2

BE2

BG 1

BF1

BD 1

BC 1

F1

AV42

AR36

BF17

M1

B28

B30

B29

C29

A28

M2 8

B2

SA_CK_0

SA_CK_1

SB_CK_0

SA_C K#_0

SA_C K#_1

SB_C K#_0

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_C S#_0

SA_C S#_1

SB_C S#_0

SB_C S#_1

SM_DRAMRST#

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

CFG_18

CFG_19

CFG_2

CFG_0

CFG_1

CFG_20

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

PM_SYNC#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

DPLL_REF_CLK

D P LL_R EF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

DM I_RXN_0

DM I_RXN_1

DM I_RXN_2

DM I_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

ME_ JTAG_ TCK

ME_ JTAG_ TDO

ME_ JTAG_ TDI

ME_ JTAG_ TM S

RSVD22

RSVD23

RSVD24

RSVD25

PM_DPRSTP#

SB_CK_1

SB_C K#_1

RSVD20

RSVD5

RSVD6

RSVD7

RSVD8

RSVD1

RSVD2

RSVD3

RSVD4

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR _EN

SM_RCOMP_VOH

SM_RCOMP_VOL

THERMTRIP#

DPRSLPVR

RSVD9

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VR EF

NC _1

NC _2

NC _3

NC _4

NC _5

NC _6

NC _7

NC _8

NC _9

NC _10

NC _11

NC _12

NC _13

NC _14

NC _15

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKR EQ#

RSVD14

ICH _SYN C#

TSATN#

PEG_CLK#

PEG_CLK

NC _16

GFX_VID_4

RSVD15

DDPC_CTRLCLK

NC _17

NC _18

NC _19

NC _20

NC _21

NC _22

NC _23

NC _24

NC _25

SM_VREF

SM_PWROK

SM_REXT

RSVD17

HDA_BCLK

HD A_RST#

HDA_SDI

HD A_SDO

HDA_SYNC

DDPC_CTRLDATA

RSVD21

M_ CK E3 1 1

PM_NC21

PM_NC15

R93 *0_04

XO R

DFGT_VID_230

DMI_TXN2 14

R110

* 2. 21K_1% _04

PEG_TXP10

PEG_RXP4

GTP10

R98 *0_04

GM_DDC_CLK28

PEG_RXP[0..15]37

GTN6

PEG_TXN2

Z05 70

C172 0.1u_10V_04

Lo w= X2

High=X4( D ef ault)

Z0503

GM_LVDS_L2N

PEG_TXP11

Z0581

R111 0_04

GM_LVDS_UC LKN

PEG_TXP[0..15]

PM_NC24

R362

* 2. 21K_1% _04

For PM

PEG_RXN12

GTN13

PEG_RXN14

R367

*4.02K_1%_04

DMI_RXP3 14

M_ ODT 2 11

MCH_ THERM 2 2

PEG_TXN12

GM_LVDS_U2 N

PEG_TXN10

C170 0.1u_10V_04

R148 100_1%_04

MCH_BSEL018

MCH_ICH _SYNC #15

GTN7

PEG_TXN11

PM_NC11

C150 0.1u_10V_04

R155 499_1%_04

GM_LVDS_L0P12

MCH_BSEL118

GM_LVDS_LC LKN12

PM_EXTTS0#

GM_LVDS_U1 N

Z0512

PEG_TXP5

PM_NC5

Z0516

GM_DAC_R28

DDR3_DRAMRST# 10,11

Z05 68

PEG_RXP9

C142 0.1u_10V_04

R120 *10K_04

3.3VS

GTN14

PM_NC13

C171 0.1u_10V_04

R365 *2.21K_1%_06

R125 10K_04

MCH_ CF G_ 1 1

GTP4

PEG_TXN3

MCH_ CF G_ 1 2

C163 0.1u_10V_04