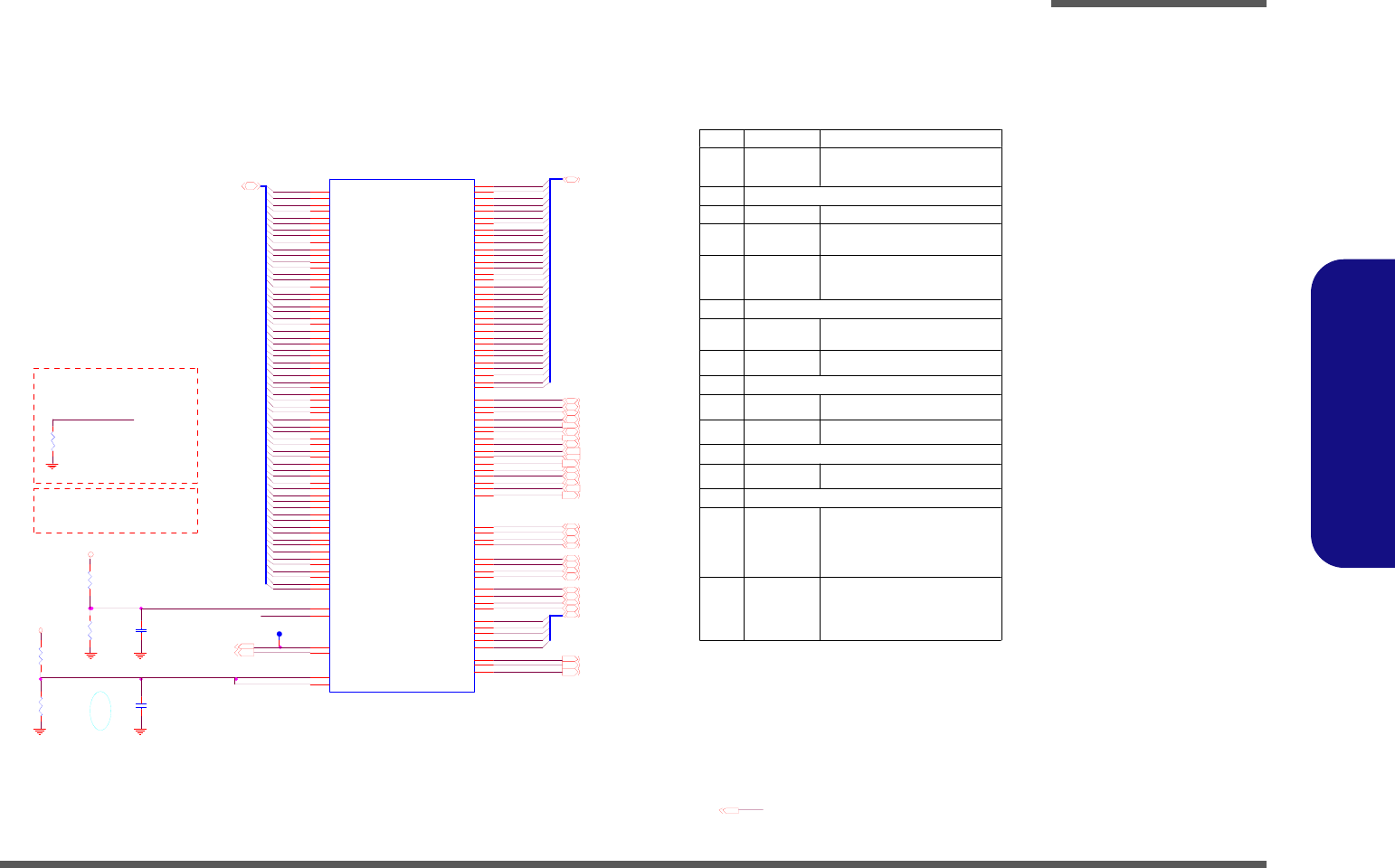

Schematic Diagrams

Cantiga 1/6, Host B - 5

B.Schematic Diagrams

Cantiga 1/6, Host

Sheet 4 of 42

Cantiga 1/6, Host

H_D#43

PCIe Gr aphics Lan e

H_D#9

CFG 6

H_CPUSLP#2

H_A#12

Low = DMI x2

High = DMI x4 (Default)

10mils

H_A#9

H_DRDY# 2

H_BR0# 2

H_D#1

H_D#7

1.05VS

H_DINV#1 2

H_REQ#[4:0]2

H_A#14

Digital Display Port

(S DVO/ DP/iHDMI )

Con curr ent with

PCIe

H_A#27

Z0401

H_A#34

H_D#20

H_D#50

H_D#28

H_BPRI# 2

CLK_MC H_BC LK 18

H_D#15

Low = Only dig ita l displ ay port ( SDV O/DP/iHDMI )

o r PCIe is operational (default)

High = Digita l d isp lay port ( SDVO/DP/iHDMI )

a nd PCIe a re op erating simultaneo usly

via t he PEG por t

H_A#24

DMI Lane Reversal

H_A#8

H_D#17

H_D#45

R95

100_1%_04

FSB Dy namic ODT

H_HITM# 2

H_D#58

H_D#39

H_D#33

H_A#33

CFG 11

Low = The ITPM Host Inter face is e nabled

High = Disabled ( Defaul t)

H_D#18

H_D#55

CFG 12

H_D#[63:0]2

H_D#0

H_D#54

1.05VS

H_D#56

Confi gur ati on

H_RE Q#4

Reserv ed

H_A#26

10 mils wide, 20 mils spacing

Low = Normal operation (Default):

L ane Numbered in Order

High = Rever se Lane s

DMI x 4 mode [( G)MCH->ICH]:

( 3->0 , 2-> 1, 1-> 2 and 0- >3)

DMI x 2 mode [( G)MCH->ICH]:

( 3->0 , 2->1)

Low = ALLZ mod e enabl ed

High = Disabled (d efaul t)

H_ADSTB#0 2

H_D#34

H_D#32

H_DSTBN#0 2

H_A#35

H_D#14

Low = XOR mo de enab led

High = Disabled (d efaul t)

H_A#5

H_D#49

H_A#11

Pi n Name

H_DSTBN#1 2

H_D#5

H_D#23

H_D#25

H_A#25

Layout Notice:

A LLZ

Low = Reve rse Lanes, 15 ->0, 1 4->1 e tc

High = Normal ope rati on ( defa ult):

L ane Numbered in Or der

H_D#48

H_RE Q#3

H_D#13

H_D#10

H_D#36

H_RS#1 2

MCH_HSWING

CFG 10

H_D#16

DMI x2 Select

H_DSTBP#2 2

H_A#19

H_RS#0 2

H_A#16

H_D#24

Reserv ed

CFG 9

H_D#3

H_C PUR ST#2

H_A#23

H_A#6

H_D#60

H_A#32

CFG 7

H_A#31

H_A#[35:3] 2

MCH_HSWING a 10 mils traces

and 20 mils spacing

H_DSTBN#3 2

H_A#13

H_D#37

Reserv ed

CFG 8

H_D#21

C136

0.1u_10V_04

H_TRDY# 2

H_D#12

H_A#7

H_A#22

CFG 4:3

H_ADS# 2

H_A#15

H_DINV#0 2

H_D#2

H_DPWR# 2

H_RE Q#2

H_D#11

Reserv ed

FSB Fr eguency

H_LOCK# 2

H_D#30

H_D#27

H_DSTBP#3 2

C128

*0.1u_10V_04

CFG 20

H_A#28

H_D#6

HOST

U25A

CAN TIGA

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

A14

B18

K17

C15

F16

H13

C18

M16

J13

H12

B16

G17

A9

F11

G12

AH6

C12

AH7

F2

F13

B13

G8

M9

L6

N10

AA8

AA2

AE11

D4

H3

B10

M11

J1

J2

N12

J6

P2

L2

R2

N9

F8

M5

J3

N2

R1

N5

N6

P13

N8

L7

E6

M3

Y3

AD14

Y6

Y10

Y12

Y14

Y7

W2

G2

Y9

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

H6

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

H2

AE8

AG2

AD6

F6

E9

J8

L3

Y13

Y1

J11

F9

L10

M7

AA 5

AE 6

L9

M8

AA 6

AE 5

A11

B11

C9

H9

E12

H11

B15

K13

B14

B20

F21

K21

L20

C5

E11

E3

B6

F12

C8

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_3

H_A#_30

H_A#_31

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_ADS#

H_AD STB#_0

H_AD STB#_1

H_BN R#

H_BPRI#

H_BR EQ#

HPLL_CLK#

H_CPU RS T#

HPLL_CLK

H_D#_0

H_REQ#_2

H_REQ#_3

H_D#_1

H_D#_10

H_D#_20

H_D#_30

H_D#_40

H_D#_50

H_D#_60

H_D#_8

H_D#_9

H_DB SY#

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_2

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_3

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_4

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_5

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_6

H_D#_61

H_D#_62

H_D#_63

H_D#_7

H_DEF ER#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DP WR#

H_D RD Y#

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DS TB P#_0

H_DS TB P#_1

H_DS TB P#_2

H_DS TB P#_3

H_AVR EF

H_DVR EF

H_TRD Y#

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_4

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_SWIN G

H_CPU SLP#

H_RC OM P

H_R S#_0

H_R S#_1

H_R S#_2

H_DEFER# 2

H_D#4

H_D#53

H_ADSTB#1 2

H_A#29

10mils

R91

1K_1%_04

H_D#63

H_D#61

H_DBSY# 2

H_D#57

H_D#62

R104

24.9_1%_04

R90

2K_1%_04

Reserv ed

H_HIT# 2

H_D#26

CFG 15: 1 4

Layout Notice:

PCIe Lo opback

enabl e

H_DSTBN#2 2

H_A#18

H_D#51

R96

221_1%_04

CFG 18: 1 7

H_DSTBP#1 2

CFG 2:0

H_D#40

H_D#47

H_A#21

CFG 13

H_A#3

H_D#19

CFG16 Low = Dyna mic ODT disabled

High = Dynamic ODT enabled ( defa ult)

H_RE Q#0

H_D#22

1.05VS2,3,5,9,13,16,18,33

H_A#17

H_D#31

CLK_MCH_BCLK# 18

CFG 5

H_DSTBP#0 2

H_D#46

H_RE Q#1

MCH _HR CO MP

Low = Enabled

High = Disabled (d efaul t)

H_D#59

H_D#35

H_D#8

000 = 10 66

010 = 80 0

011 = 66 7

Others = Reserved

D VT: De l C1 27

H_D#38

Low = Intel Ma nagement Engine Cr ypto T ransp ort Layer

Secur ity (TLS) ciph er sui te with no confidenti ali ty

High = Intel Manag ement Engine Crypto TLS cipher suite

w ith conf id entiality ( def ault)

H_D#52

H_A#30

H_BNR# 2

H_A#4

In tegra ted Tr usted

Platfor m Module(ITPM)

Host Interface

100mil

H_D#44

H_D#41

MCH_HRCOMP

XO R

H_D#42

Intel Ma nagement

Engine Crypto

Strap

H_RS#2 2

H_DINV#2 2

Str ap Descripti on

CFG 19

H_DINV#3 2

H_A#20

H_A#10

H_D#29