CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E Page 23 of 68

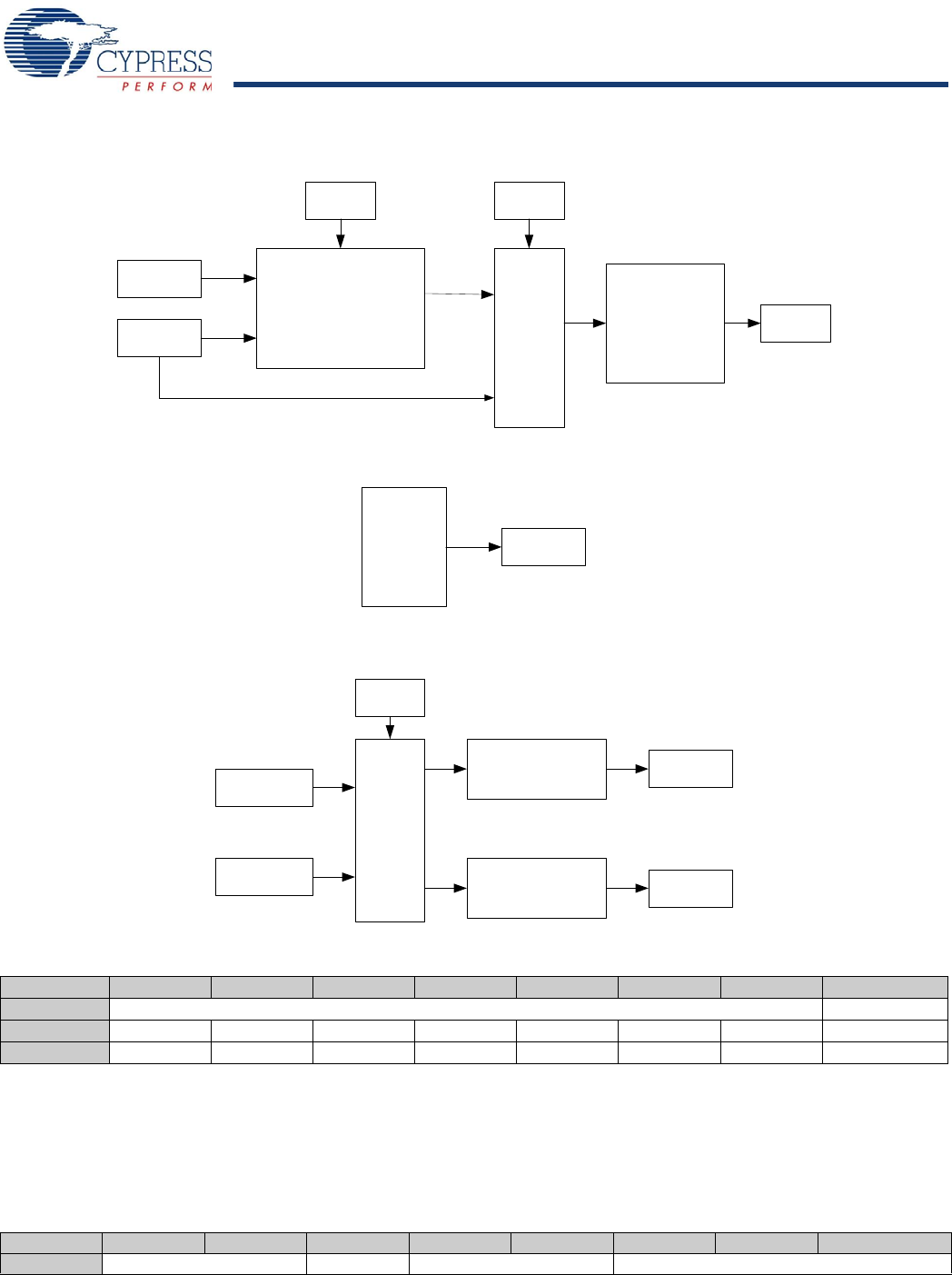

Figure 12-1. CPU Clock Block Diagram

SCALE

(divide by 2

n,

n = 0-5,7)

MUX

CLK_EXT

CLK_24MHz

CPUCLK

SEL

CLK_CPU

Doubler CLK_HS

LP OSC

32-KHz

CLK_32KHz

XTAL OSC

1-24MHz

CY7C601xx only

MUX

Crystal Oscillator Disabled

XOSC

SEL

EN

CLK_EXTEFTB

P0.0

CLKIN

P0.1

CLKOUT

CY7C601xx

only

Table 12-2. CPU Clock Configuration (CPUCLKCR) [0x30] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field Reserved CPUCLK Select

Read/Write – – – – – – – R/W

Default 0 0 0 0 0 0 0 0

Bit [7:1]: Reserved

Bit 0: CPU CLK Select

0 = Internal 24 MHz Oscillator

1 = External oscillator source

Note The CPU speed selection is configured using the OSC_CR0 Register (Table 12-3).

Table 12-3. OSC Control 0 (OSC_CR0) [0x1E0] [R/W]

Bit # 7 6 5 4 3 2 1 0

Field Reserved No Buzz Sleep Timer [1:0] CPU Speed [2:0]

[+] Feedback [+] Feedback