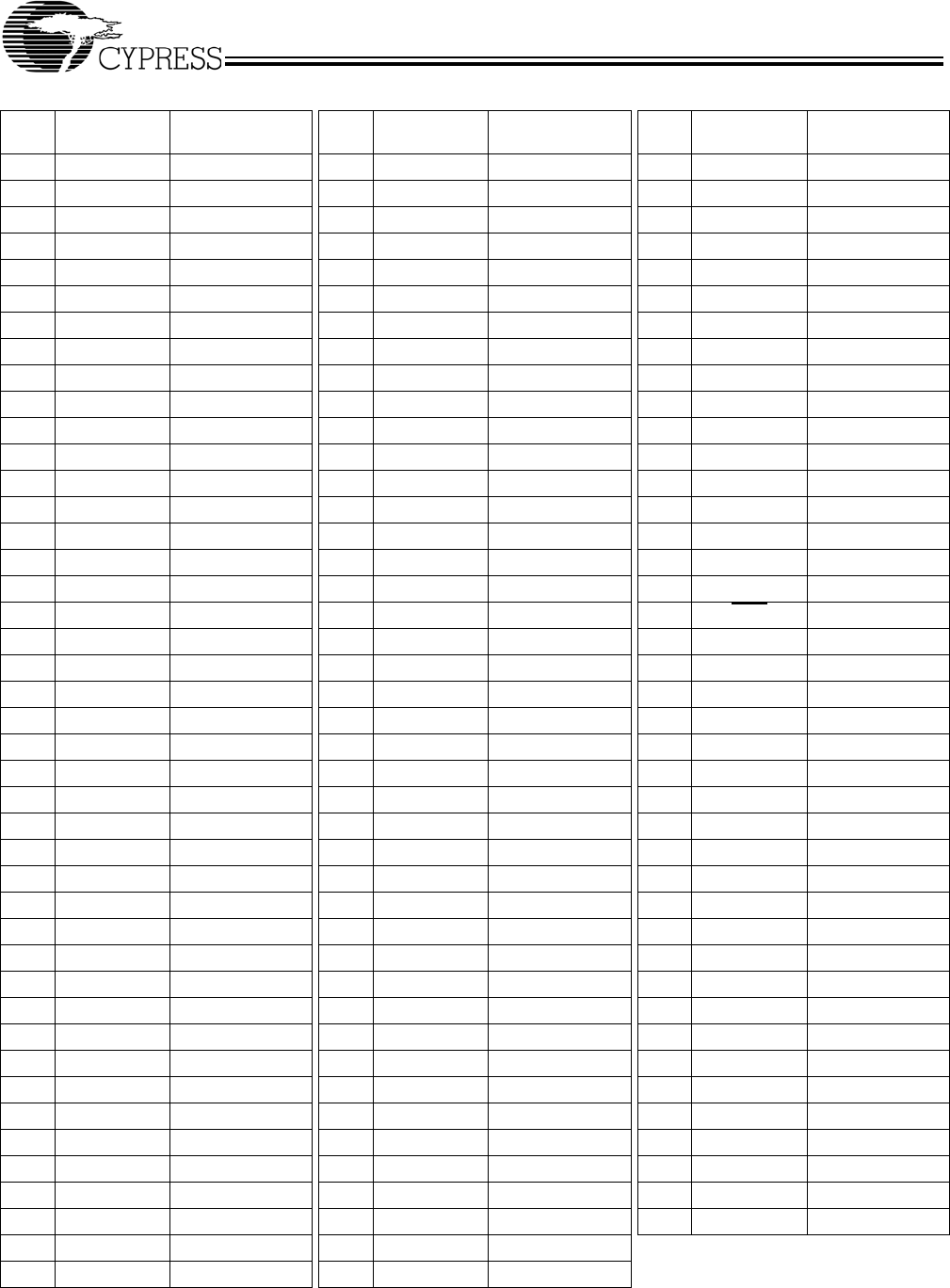

CYV15G0104TRB

Document #: 38-02100 Rev. *B Page 25 of 27

C04 VCC POWER F02 NC NO CONNECT L20 GND GROUND

C05 VCC POWER F03 VCC POWER M01 NC NO CONNECT

C06 NC NO CONNECT F04 NC NO CONNECT M02 NC NO CONNECT

M03 NC NO CONNECT U03 TXDB[2] LVTTL IN W03 NC NO CONNECT

M04 NC NO CONNECT U04 TXDB[9] LVTTL IN W04 NC NO CONNECT

M17 NC NO CONNECT U05 VCC POWER W05 VCC POWER

M18 NC NO CONNECT U06 NC NO CONNECT W06 NC NO CONNECT

M19 NC NO CONNECT U07 NC NO CONNECT W07 NC NO CONNECT

M20 GND GROUND U08 GND GROUND W08 GND GROUND

N01 GND GROUND U09 GND GROUND W09 ADDR [2] LVTTL IN PU

N02 GND GROUND U10 ADDR [0] LVTTL IN PU W10 ADDR [1] LVTTL IN PU

N03 GND GROUND U11 REFCLKB– PECL IN W11 RXCLKA+ LVTTL OUT

N04 GND GROUND U12 GND GROUND W12 REPDOA LVTTL OUT

N17 GND GROUND U13 GND GROUND W13 GND GROUND

N18 GND GROUND U14 GND GROUND W14 GND GROUND

N19 GND GROUND U15 VCC POWER W15 VCC POWER

N20 GND GROUND U16 VCC POWER W16 VCC POWER

P01 NC NO CONNECT U17 RXDA[4] LVTTL OUT W17 LFIA

LVTTL OUT

P02 NC NO CONNECT U18 VCC POWER W18 TRGCLKA+ PECL IN

P03 NC NO CONNECT U19 BISTSTA LVTTL OUT W19 RXDA[6] LVTTL OUT

P04 NC NO CONNECT U20 RXDA[0] LVTTL OUT W20 RXDA[3] LVTTL OUT

P17 GND GROUND V01 TXDB[3] LVTTL IN Y01 TXDB[6] LVTTL IN

P18 GND GROUND V02 TXDB[4] LVTTL IN Y02 TXCLKB LVTTL IN PD

P19 GND GROUND V03 TXDB[8] LVTTL IN Y03 NC NO CONNECT

P20 GND GROUND V04 NC NO CONNECT Y04 NC NO CONNECT

R01 NC NO CONNECT V05 VCC POWER Y05 VCC POWER

R02 NC NO CONNECT V06 NC NO CONNECT Y06 NC NO CONNECT

R03 NC NO CONNECT V07 NC NO CONNECT Y07 NC NO CONNECT

R04 NC NO CONNECT V08 GND GROUND Y08 GND GROUND

R17 VCC POWER V09 NC NO CONNECT Y09 TXCLKOB LVTTL OUT

R18 VCC POWER V10 GND GROUND Y10 NC NO CONNECT

R19 VCC POWER V11 REFCLKB+ PECL IN Y11 GND GROUND

R20 VCC POWER V12 RECLKOA LVTTL OUT Y12 RXCLKA– LVTTL OUT

T01 VCC POWER V13 GND GROUND Y13 GND GROUND

T02 VCC POWER V14 GND GROUND Y14 GND GROUND

T03 VCC POWER V15 VCC POWER Y15 VCC POWER

T04 VCC POWER V16 VCC POWER Y16 VCC POWER

T17 VCC POWER V17 RXDA[9] LVTTL OUT Y17 TXERRB LVTTL OUT

T18 VCC POWER V18 RXDA[5] LVTTL OUT Y18 TRGCLKA– PECL IN

T19 VCC POWER V19 RXDA[2] LVTTL OUT Y19 RXDA[8] LVTTL OUT

T20 VCC POWER V20 RXDA[1] LVTTL OUT Y20 RXDA[7] LVTTL OUT

U01 TXDB[0] LVTTL IN W01 TXDB[5] LVTTL IN

U02 TXDB[1] LVTTL IN W02 TXDB[7] LVTTL IN

Table 7. Package Coordinate Signal Allocation (continued)

Ball

ID Signal Name Signal Type

Ball

ID Signal Name Signal Type

Ball

ID Signal Name Signal Type

[+] Feedback