CYV15G0104TRB

Document #: 38-02100 Rev. *B Page 3 of 27

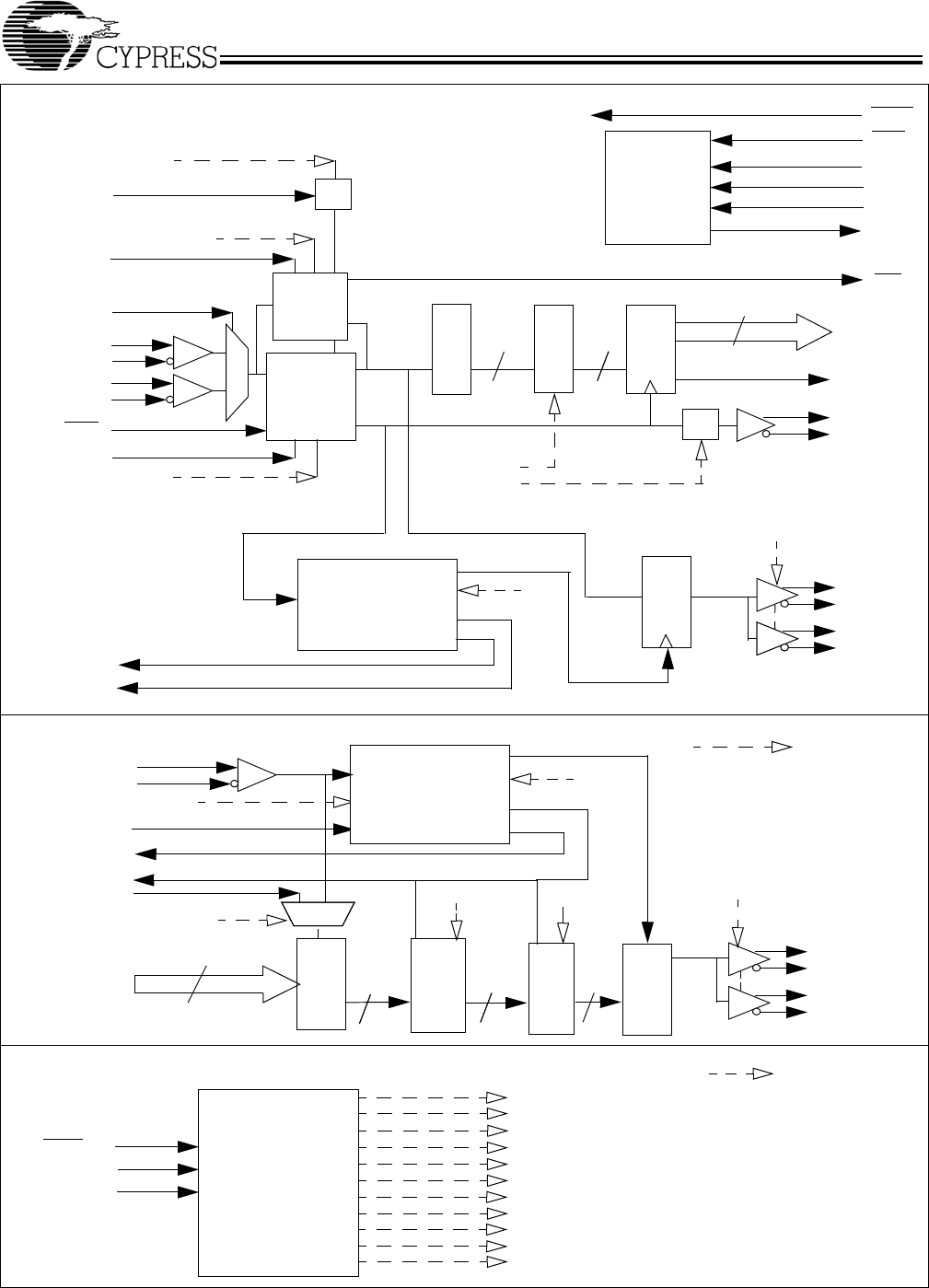

INA1+

INA1–

INA2+

INA2–

INSELA

Clock &

Data

Recovery

PLL

Shifter

LFIA

10

RXDA[9:0]

Receive

Signal

Monitor

Output

Register

RXCLKA+

RXCLKA–

÷2

JTAG

Boundary

Scan

Controller

TDO

TMS

TCLK

TDI

RESET

Reclocking Deserializer Path Block Diagram

TRST

RXPLLPDA

SPDSELA

ULCA

RXRATEA

10

BIST LFSR

10

RXBISTA[1:0]

LDTDEN

SDASEL[2..1]A[1:0]

ROUTA1+

ROUTA1–

ROUTA2+

ROUTA2–

ROE[2..1]A

Bit-Rate Clock

Character-Rate Clock

Reclocker

RECLKOA

Register

Recovered Character Clock

Recovered Serial Data

TRGCLKA

x2

TRGRATEA

REPDOA

BISTSTA

Clock Multiplier

Output PLL

ROE[2..1]A

Shifter

Serializer Path Block Diagram

TXRATEB

Input

Register

Phase-Align

Buffer

SPDSELB

REFCLKB+

REFCLKB–

Transmit PLL

Clock Multiplier

TXCLKB

Bit-Rate Clock

Character-Rate Clock

TOUTB1+

TOUTB1–

TOUTB2+

TOUTB2–

Phase-Align

Buffer

Transmit PLL

Clock Multiplier

TOE[2..1]B

TXCKSELB

= Internal Signal

TXERRB

TXCLKOB

TXDB[9:0]

10

10

PABRSTB

TOE[2..1]B

10

BIST LFSR

10

TXBISTB

10

WREN

ADDR[2:0]

DATA[6:0]

Device Configuration and Control Block Diagram

= Internal Signal

RXRATEA

RXPLLPDA

TXRATEB

TXCKSELB

TOE[2..1]B

PABRSTB

Device Configuration

and Control Interface

SDASEL[2..1]A[1:0]

RXBISTA[1:0]

TXBISTB

ROE[2..1]A

TRGRATEA

[+] Feedback