EM78612

Universal Serial Bus Microcontroller

Product Specification (V1.0) 03.22.2006 •

••

• 33

(This specification is subject to change without further notice)

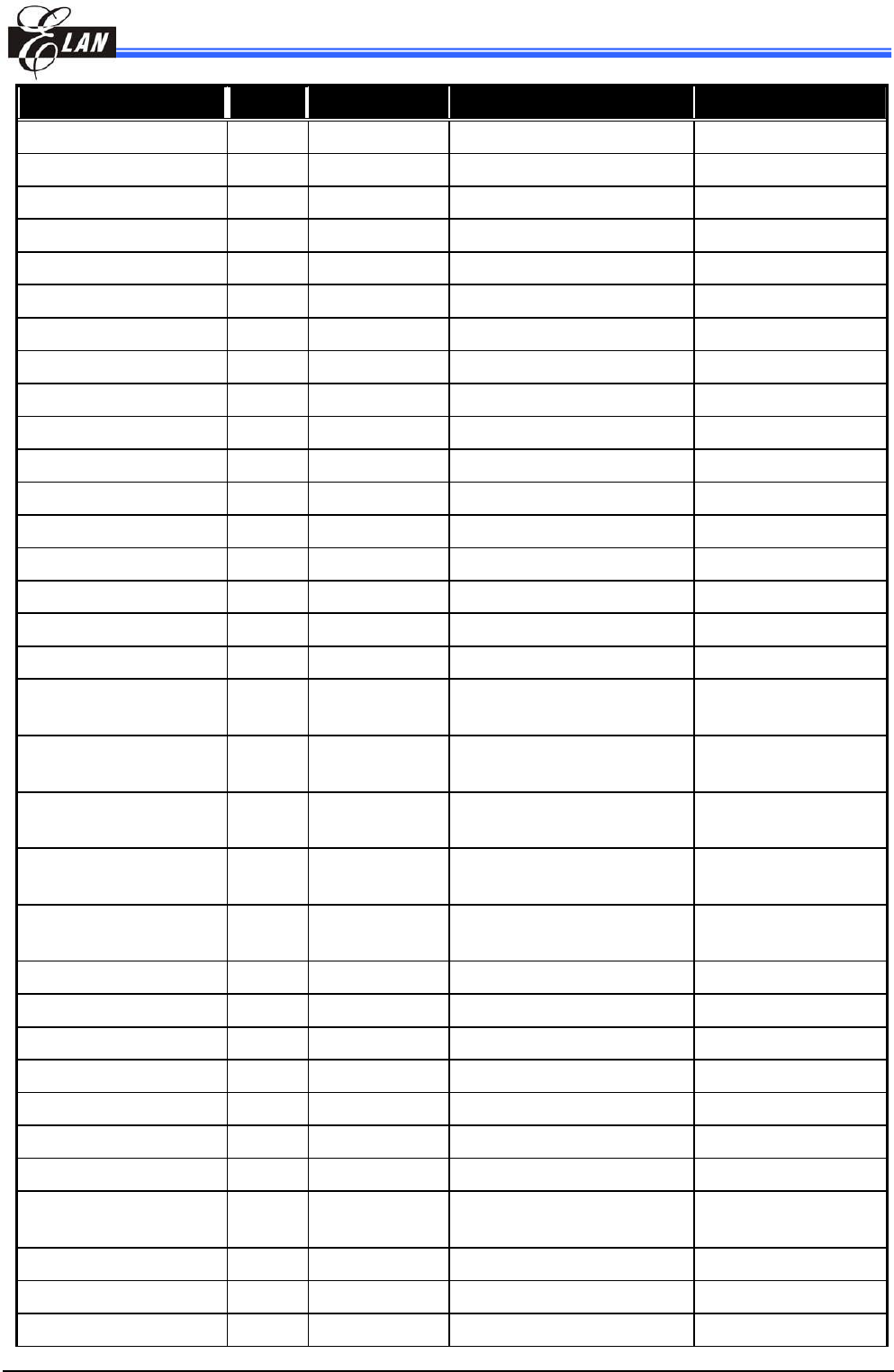

INSTRUCTION BINARY HEX MNEMONIC OPERATION STATUS AFFECTED

0 0001 11rr rrrr 01rr DEC R R-1 → R Z

0 0010 00rr rrrr 02rr OR A,R A ∨ VR → A Z

0 0010 01rr rrrr 02rr OR R,A A ∨ VR → R Z

0 0010 10rr rrrr 02rr AND A,R A & R → A Z

0 0010 11rr rrrr 02rr AND R,A A & R → R Z

0 0011 00rr rrrr 03rr XOR A,R A ⊕ R → A Z

0 0011 01rr rrrr 03rr XOR R,A A ⊕ R → R Z

0 0011 10rr rrrr 03rr ADD A,R A + R → A Z,C,DC

0 0011 11rr rrrr 03rr ADD R,A A + R → R Z,C,DC

0 0100 00rr rrrr 04rr MOV A,R R → A Z

0 0100 01rr rrrr 04rr MOV R,R R → R Z

0 0100 10rr rrrr 04rr COMA R /R → A Z

0 0100 11rr rrrr 04rr COM R /R → R Z

0 0101 00rr rrrr 05rr INCA R R+1 → A Z

0 0101 01rr rrrr 05rr INC R R+1 → R Z

0 0101 10rr rrrr 05rr DJZA R R-1 → A, skip if zero None

0 0101 11rr rrrr 05rr DJZ R R-1 → R, skip if zero None

0 0110 00rr rrrr 06rr RRCA R

R(n) → A(n-1),

R(0) → C, C → A(7)

C

0 0110 01rr rrrr 06rr RRC R

R(n) → R(n-1),

R(0) → C, C → R(7)

C

0 0110 10rr rrrr 06rr RLCA R

R(n) → A(n+1),

R(7) → C, C → A(0)

C

0 0110 11rr rrrr 06rr RLC R

R(n) → R(n+1),

R(7) → C, C → R(0)

C

0 0111 00rr rrrr 07rr SWAPA R

R(0-3) → A(4-7),

R(4-7) → A(0-3)

None

0 0111 01rr rrrr 07rr SWAP R R(0-3) ↔ R(4-7) None

0 0111 10rr rrrr 07rr JZA R R+1 → A, skip if zero None

0 0111 11rr rrrr 07rr JZ R R+1 → R, skip if zero None

0 100b bbrr rrrr 0xxx BC R,b 0 → R(b) None <Note2>

0 101b bbrr rrrr 0xxx BS R,b 1 → R(b) None

0 110b bbrr rrrr 0xxx JBC R,b if R(b)=0, skip None

0 111b bbrr rrrr 0xxx JBS R,b if R(b)=1, skip None

1 00kk kkkk kkkk 1kkk CALL k

PC+1 → [SP],

(Page, k) → PC

None

1 01kk kkkk kkkk 1kkk JMP k (Page, k) → PC None

1 1000 kkkk kkkk 18kk MOV A,k k → A None

1 1001 kkkk kkkk 19kk OR A,k A ∨ k → A Z