Advanced/ZP Technical Product Summary • Page 17

Appendix C − I/O Map

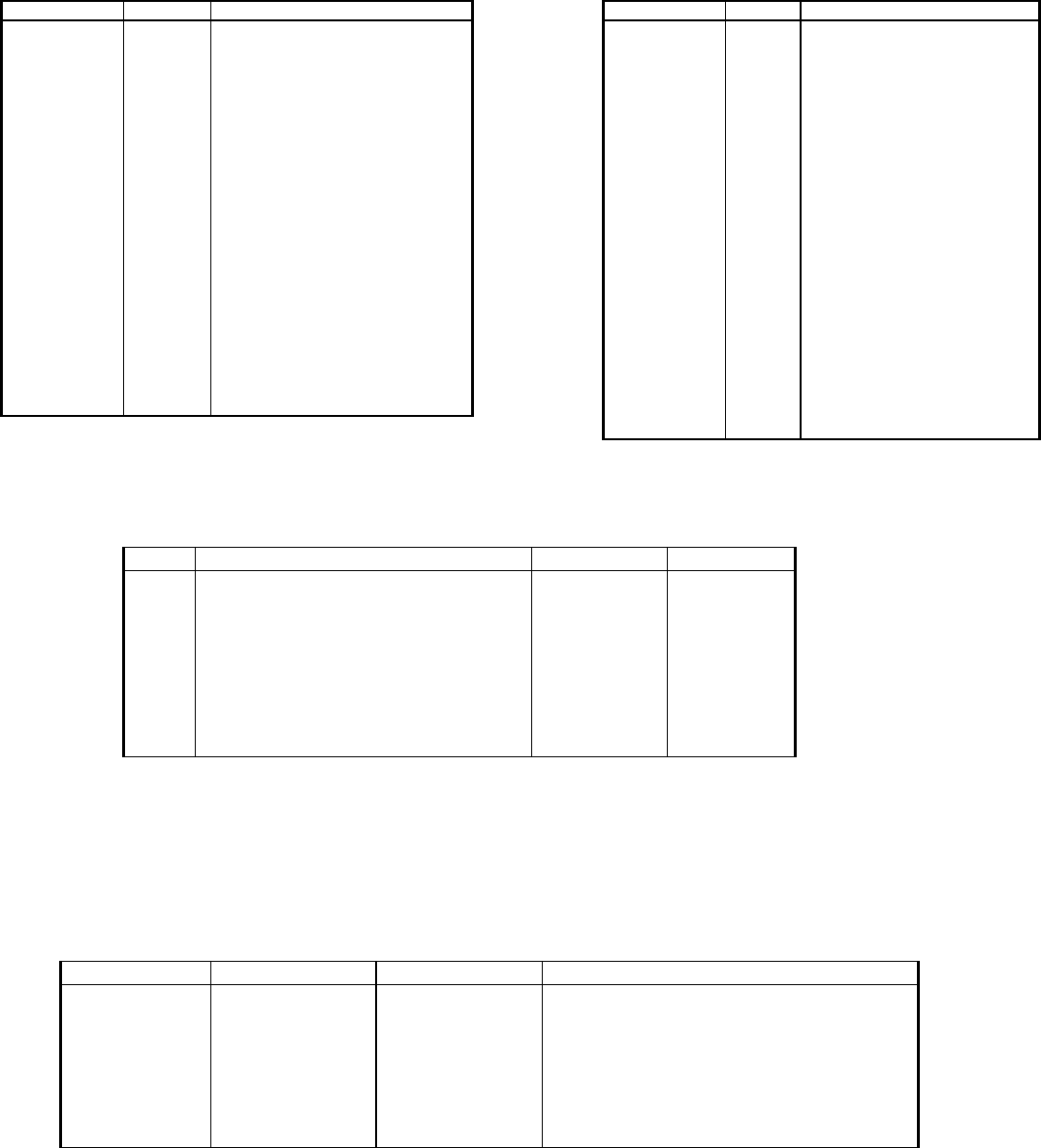

Address (hex) Size Description

0000 - 000F 16 bytes PIIX - DMA 1

0020 - 0021 2 bytes PIIX - Interrupt Controller 1

0040 - 0043 4 bytes PIIX - Timer 1

0048 - 004B 4 bytes PIIX - Timer 2

0060 1 byte Keyboard Controller Data Byte

0061 1 byte PIIX - NMI, speaker control

0064 1 byte Kbd Controller, CMD/STAT

0070, bit 7 1 bit PIIX - Enable NMI

0070, bits 6:0 7 bits PIIX - Real Time Clock, Address

0071 1 byte PIIX - Real Time Clock, Data

0078 1 byte Reserved - Brd. Config.

0079 1 byte Reserved - Brd. Config. RD Only

0080 - 008F 16 bytes PIIX - DMA Page Register

00A0 - 00A1 2 bytes PIIX - Interrupt Controller 2

00C0 - 00DE 31 bytes PIIX - DMA 2

00F0 1 byte Reset Numeric Error

0170 - 0177 8 bytes Secondary IDE Channel

Address (hex) Size Description

01F0 - 01F7 8 bytes Primary IDE Channel

0278 - 027B 4 bytes Parallel Port 2

02F8 - 02FF 8 bytes On-Board Serial Port 2

0376 1 byte Sec IDE Chan Cmd Port

0377 1 byte Sec IDE Chan Stat Port

0378 - 037F 8 bytes Parallel Port 1

03BC - 03BF 4 bytes Parallel Port x

03E8 - 03EF 8 bytes Serial Port 3

03F0 - 03F5 6 bytes Floppy Channel 1

03F6 1 bytes Pri IDE Channel Cmnd Port

03F7 (Write) 1 byte Floppy Channel 1 Command

03F7, bit 7 1 bit Floppy Disk Change Channel 1

03F7, bits 6:0 7 bits Pri IDE Channel Status Port

03F8 - 03FF 8 bytes On-Board Serial Port 1

LPT + 400h 8 bytes ECP port, LPT + 400h

0CF8-0CFB* 4 bytes PCI Config Addr Reg Enable

0CFC-0CFF* 4 bytes PCI Config Data Reg

FF00-FF07 8 bytes IDE Bus Master Reg.

Table C-1 and C-2. Advanced/ZP I/O Address Map

* Only accessible after PCI configuration space is enabled.

I/O Port 78 is reserved for BIOS use. I/O Port 79 is a read only port, the bit definitions are shown below.

Bit # Description Bit = 1 Bit = 0

0 Internal CPU Clock Freq. (Switch 6) 3/2x 2x

1 No Connect

2 No Connect

3 External CPU clock (Switch 7)

4 External CPU clock (Switch 8)

5 Setup Disable (Switch 5) Enable access Disable access

6 Clear CMOS (Switch 4) Keep values Clear values

7 Password Clear (Switch 3) Keep password Clear password

Figure C-3. I/O Port For Board Configuration

PCI CONFIGURATION SPACE MAP

The Triton chipset uses Configuration Mechanism 1 to access PCI configuration space. The PCI Configuration Address

register is a 32-bit register located at CF8h, the PCI Configuration Data register is a 32-bit register located at CFCh. These

registers are only accessable by full DWORD accesses. The table below lists the PCI bus and device numbers used by the

baseboard.

Bus Number (hex) Dev Number (hex) Func. Number (hex) Description

00 00 00 Intel 82437FX (TSC)

00 07 00 Intel 82371FB (PIIX) PCI/ISA bridge

00 07 01 Intel 82371FB (PIIX) IDE Bus Master

00 0F PCI Expansion Slot 1

00 0D PCI Expansion Slot 2

00 0E PCI Expansion Slot 3

00 10 PCI Expansion Slot 4

Table C-4. Advanced/ZP PCI Config. Space Map