Software Developer’s Manual 245

Register Descriptions

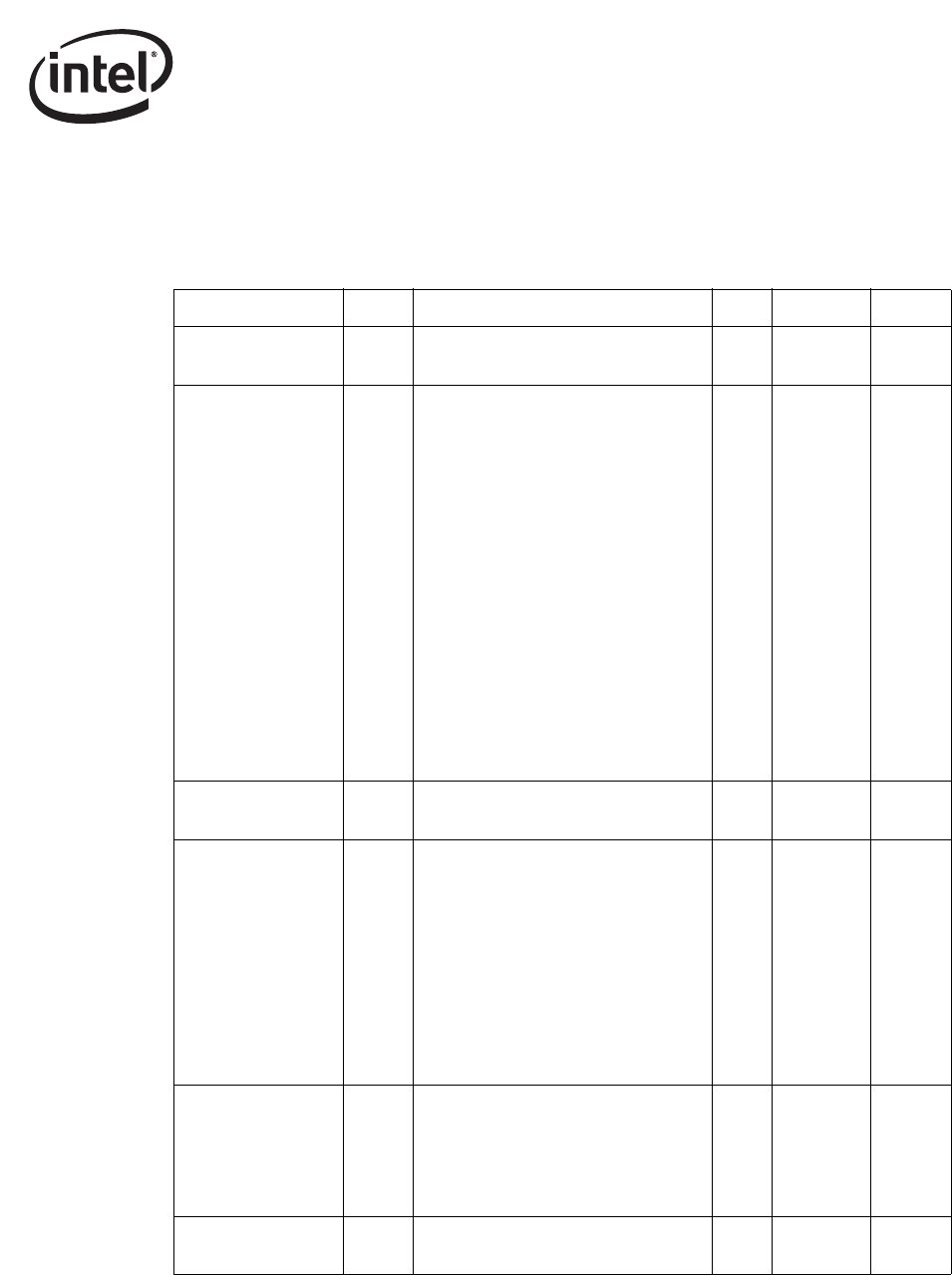

13.4.7.1.1 PHY Control Register

PCTRL (00d; R/W)

Table 13-16. PHY Control Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Reserved 5:0

These bits are reserved and should be

set to 000000b.

RO

RW

1

Always

000000b

Speed Selection

(MSB)

6

Speed Selection is determined by bits 6

(MSB) and 13 (LSB) as follows.

11b = Reserved

10b = 1000 Mbps

01b = 100 Mbps

00b = 10 Mbps

A write to these bits do not take effect

until a software reset is asserted,

Restart Auto-Negotiation is asserted, or

Power Down transitions from power

down to normal operation.

82544GC/EI only:

The Speed Selection bits take on the

values set by external pins ANEG[3:0]

on hardware reset only.

Bit 6: ANEG[3] | ANEG[2] | (MODE[3:0]

is one of xx01b, 1x00b, 001xb, 0111b).

Bit 13: (ANEG[3:1] = 001b) and

(MODE[3:0] is not any of xx01b, 1x00b,

001xb, 0111b).

R/W 1b

ANEG[3:2]

MODE[3:0]

Update

Collision Test 7

1b = Enable COL signal test.

0b = Disable COL signal test.

R/W 0b 0b

Duplex Mode 8

1b = Full Duplex.

0b = Half Duplex.

82544GC/EI only:

The Duplex bit takes on the value set by

external pins ANEG[3:2, 0] on hardware

reset only.

Bit 8: ANEG[3:2,0] = 001 | ANEG[3].

A write to this bit does not take effect

until a software reset is asserted,

Restart Auto-Negotiation is asserted, or

Power Down transitions from power

down to normal power.

R/W

1b

ANEG[3:2,

0]

Update

Restart Auto-

Negotiation

9

1b = Restart Auto-Negotiation Process.

0b = Normal operation.

Auto-Negotiation automatically restarts

after hardware or software reset

regardless of whether or not the restart

bit is set.

R/W,

SC

0b

Self

Clear

Isolate 10

1b = Isolate.

0b = Normal operation.

R/W 0b 0b