Receive and Transmit Description

Software Developer’s Manual 45

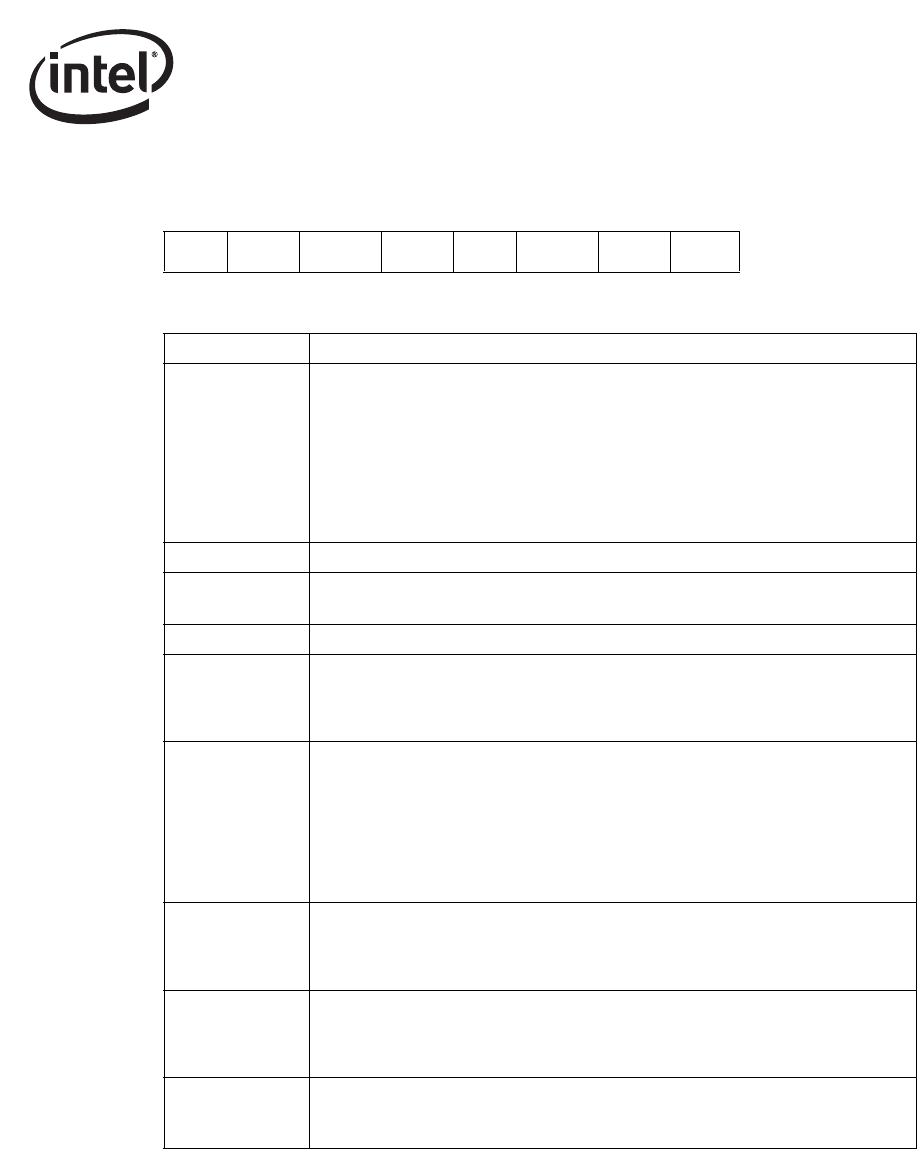

Table 3-15. Command Field (TDESC.TUCMD) Layout

Note:

1. The IDE, DEXT, and RS bits are valid regardless of the state of TSE. All other bits are ignored

if TSE = 0b.

2. The TCP Segmentation feature also provides access to a generic block send function and may

be useful for performing “segmentation offload” in which the header information is constant.

By clearing both the TCP and IP bits, a block of data may be broken down into frames of a

given size, a constant, arbitrary length header may be pre-pended to each frame, and two

checksums optionally added.

7 6 5 4 3 2 1 0

IDE RSV DEXT RSV RS TSE IP TCP

TDESC.TUCMD Description

IDE (bit 7)

Interrupt Delay Enable

IDE activates the transmit interrupt delay timer. Hardware loads a countdown

register when it writes back a transmit descriptor that has the RS bit and the IDE bit

set. The value loaded comes from the IDV field of the Interrupt Delay (TIDV) register.

When the count reaches 0, a transmit interrupt occurs. Hardware always loads the

transmit interrupt counter whenever it processes a descriptor with IDE set even if it is

already counting down due to a previous descriptor. If hardware encounters a

descriptor that has RS set, but not IDE, it generates an interrupt immediately after

writing back the descriptor. The interrupt delay timer is cleared.

RSV (Bit 6) Reserved. Set to 0b for future compatibility.

DEXT(Bit 5)

Descriptor Extension

Must be 1b for this descriptor type.

RSV (Bit 4) Reserved. Set to 0b for future compatibility.

RS (Bit 3)

Report Status

RS tells the hardware to report the status information for this descriptor. Because this

descriptor does not transmit data, only the DD bit in the status word is valid. Refer to

Section 3.3.6.2 for the layout of the status field.

TSE (Bit 2)

TCP Segmentation Enable

TSE indicates that this descriptor is setting the TCP segmentation context. If this bit

is not set, the checksum offloading context for normal (non-”TCP Segmentation”)

packets is written. When a descriptor of this type is processed the Ethernet controller

immediately updates the context in question (TCP Segmentation or checksum

offloading) with values from the descriptor. This means that if any normal packets or

TCP Segmentation packets are in progress (a descriptor with EOP set has not been

received for the given context), the results are likely to be undesirable.

IP (Bit 1)

Packet Type (IPv4 = 1b, IPv6 = 0b)

Identifies what type of IP packet is used in the segmentation process. This is

necessary for hardware to know where the IP Payload Length field is located. This

does not override the checksum insertion bit, IXSM.

IP (Bit 1)

82544GC/EI only

Packet Type (IP = 1b)

Identifies the packet as an IP packet. The purpose of this bit is to enable/disable the

updating of the IP header during the segmentation process. This does not override

the checksum insertion bit, IXSM.

TCP (bit 0)

Packet Type (TCP = 1b)

Identifies the packet as either TCP or UDP (non-TCP). This affects the processing of

the header information.