Software Developer’s Manual 347

Register Descriptions

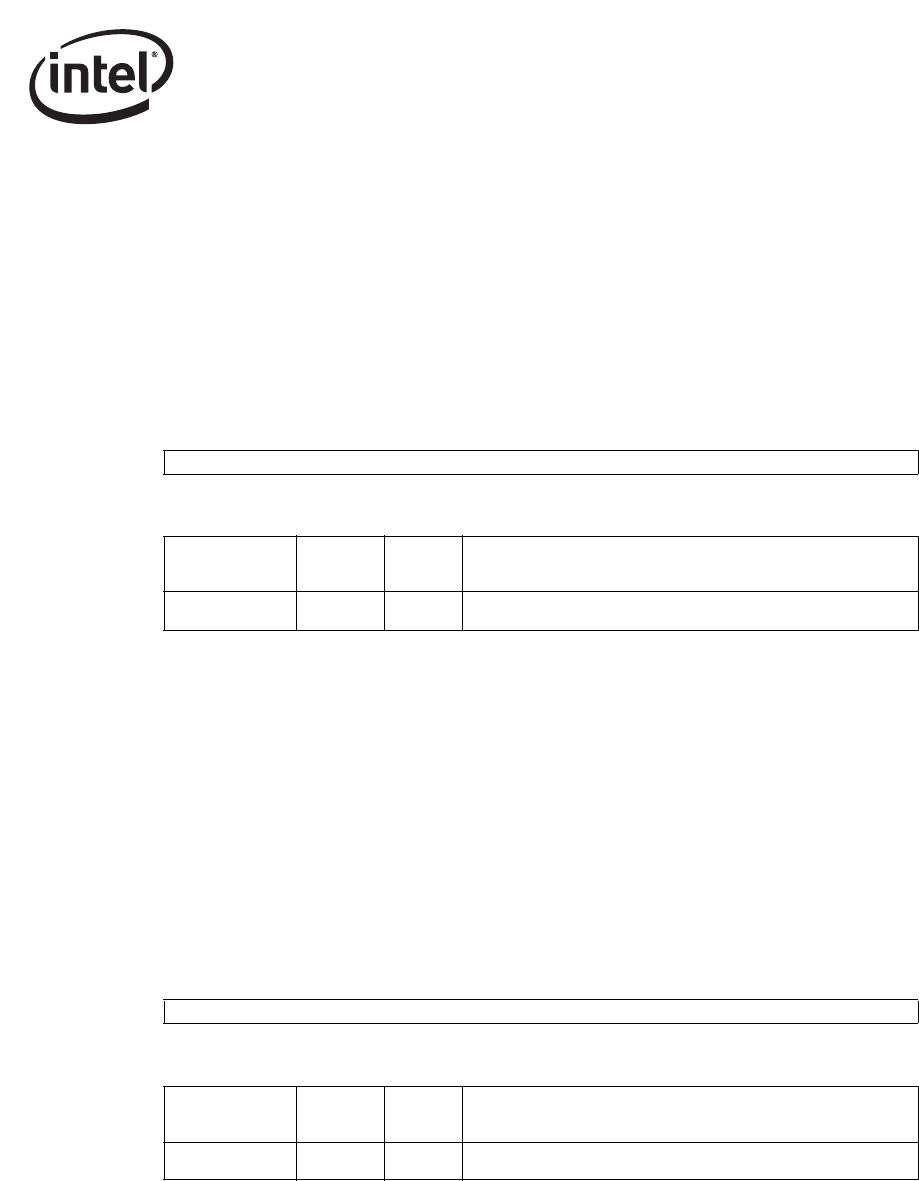

13.7.13 Sequence Error Count

SEC (04038h; R)

This register counts sequence error events. The proper sequence of 8b/10b symbols is as follows:

idle, start-of-frame (SOF), data, pad (optional), end-of-frame (EOF), fill (optional), idle. Hardware

increments this counter for any illegal sequence of delimiters. If the link is not up, this register does

not increment. This register is only valid in internal SerDes mode (TBI mode for the

82544GC/

EI

).

Table 13-105. SEC Register Bit Description

13.7.14 Carrier Extension Error Count

CEXTERR (0403Ch; R)

This register counts the number of packets received in which the carrier extension error was

signaled across the internal PHY interface. The PHY propagates carrier extension errors to the

MAC when an error is detected during the carrier extended time of a packet reception. An

extension error is signaled by the PHY by the encoding of 1Fh on the receive data inputs. This

register only increments if receives are enabled and the Ethernet controller is operating at

1000 Mb/s. For example, internal PHY or internal SerDes modes (internal PHY or TBI modes for

the

82544GC/EI).

Table 13-106. CEXTERR Register Bit Description

31 0

SEC

Field Bit(s)

Initial

Value

Description

SEC 31:0 0b Number of sequence error events.

31 0

CEXTERR

Field Bit(s)

Initial

Value

Description

CEXTERR 31:0 0b Number of packets received with a carrier extension error.