Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 27

Datasheet Volume One

Interfaces

2.2.1.1 Transaction Layer

The upper layer of the PCI Express* architecture is the Transaction Layer. The

Transaction Layer's primary responsibility is the assembly and disassembly of

Transaction Layer Packets (TLPs). TLPs are used to communicate transactions, such as

read and write, as well as certain types of events. The Transaction Layer also manages

flow control of TLPs.

2.2.1.2 Data Link Layer

The middle layer in the PCI Express* stack, the Data Link Layer, serves as an

intermediate stage between the Transaction Layer and the Physical Layer.

Responsibilities of Data Link Layer include link management, error detection, and error

correction.

The transmission side of the Data Link Layer accepts TLPs assembled by the

Transaction Layer, calculates and applies data protection code and TLP sequence

number, and submits them to Physical Layer for transmission across the Link. The

receiving Data Link Layer is responsible for checking the integrity of received TLPs and

for submitting them to the Transaction Layer for further processing. On detection of TLP

error(s), this layer is responsible for requesting retransmission of TLPs until information

is correctly received, or the Link is determined to have failed. The Data Link Layer also

generates and consumes packets which are used for Link management functions.

2.2.1.3 Physical Layer

The Physical Layer includes all circuitry for interface operation, including driver and

input buffers, parallel-to-serial and serial-to-parallel conversion, PLL(s), and impedance

matching circuitry. It also includes logical functions related to interface initialization and

maintenance. The Physical Layer exchanges data with the Data Link Layer in an

implementation-specific format, and is responsible for converting this to an appropriate

serialized format and transmitting it across the PCI Express* Link at a frequency and

width compatible with the remote device.

2.2.2 PCI Express* Configuration Mechanism

The PCI Express* link is mapped through a PCI-to-PCI bridge structure.

PCI Express* extends the configuration space to 4096 bytes per-device/function, as

compared to 256 bytes allowed by the Conventional PCI Specification. PCI Express*

configuration space is divided into a PCI-compatible region (which consists of the first

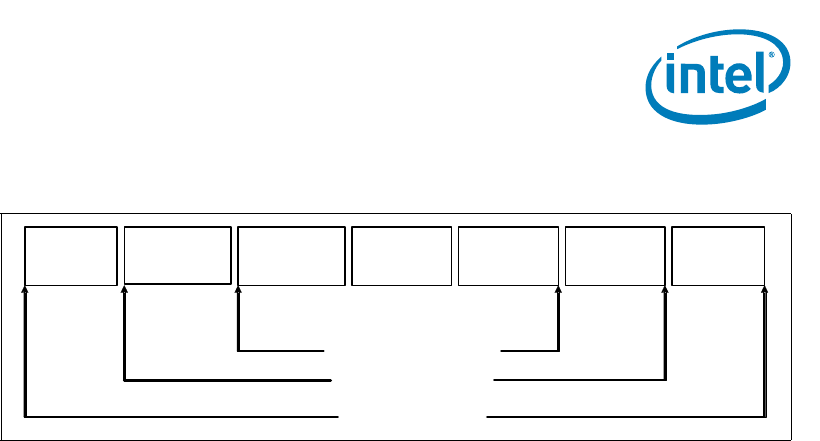

Figure 2-2. Packet Flow through the Layers

Framing

Sequence

Number

Header Data LCRCECRC Framing

Transaction Layer

Physical Layer

Data Link Layer