Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 63

Datasheet Volume One

Notes:

1. The IA32_MC0_MISC register details will be available upon implementation in a future processor stepping.

2. The MCi_ADDR and MCi_MISC registers for machine check banks 2 & 4 are not implemented on the processors. The MCi_CTL

register for machine check bank 2 is also not implemented.

3. The PECI host must determine the total number of machine check banks and the validity of the MCi_ADDR and MCi_MISC

register contents prior to issuing a read to the machine check bank similar to standard machine check architecture

enumeration and accesses.

4. The information presented in Table 2-11 is applicable to the processor only. No association between bank numbers and logical

functions should be assumed for any other processor devices (past, present or future) based on the information presented in

Table 2-11.

5. The processor machine check banks 4 through 19 reside in the processor uncore and hence will return the same value

independent of the processor ID used to access these banks.

6. The IA32_MCG_STATUS, IA32_MCG_CONTAIN and IA32_MCG_CAP are located in the uncore and will return the same value

independent of the processor ID used to access them.

7. The processor machine check banks 0 through 3 are core-specific. Since the processor ID is thread-specific and not core-

specific, machine check banks 0 through 3 will return the same value for a particular core independent of the thread

referenced by the processor ID.

8. PECI accesses to the machine check banks may not be possible in the event of a core hang. A warm reset of the processor

may be required to read any sticky machine check banks.

9. Valid processor ID values may be obtained by using the enumeration methods described in Section 2.5.2.7.2.

10. Reads to a machine check bank within a core or thread that is disabled will return all zeroes with a completion code of 0x90.

11. For SKUs where Intel QPI is disabled or absent, reads to the corresponding machine check banks will return all zeros with a

completion code of 0x40.

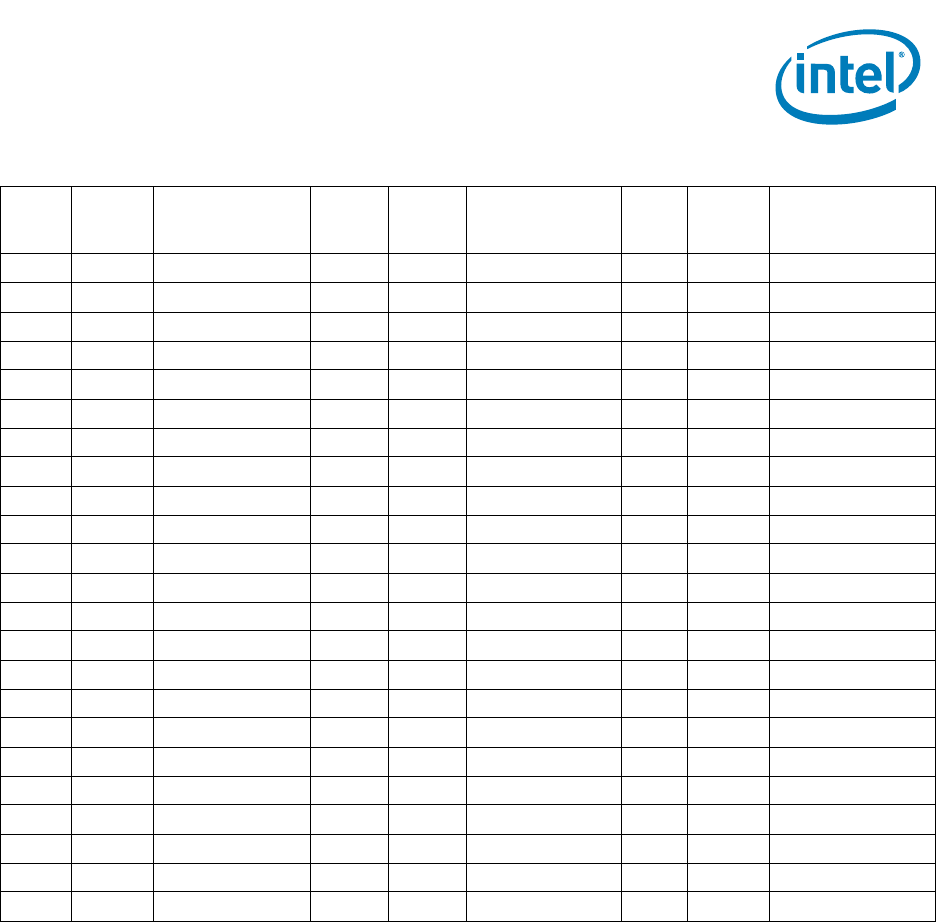

0x0-0xF 0x0282 IA32_MC2_CTL2 0x0-0xF 0x0424 IA32_MC9_CTL 0x0-0xF 0x043F IA32_MC15_MISC

0x0-0xF 0x0409 IA32_MC2_STATUS 0x0-0xF 0x0289 IA32_MC9_CTL2 0x0-0xF 0x0440 IA32_MC16_CTL

0x0-0xF 0x040A IA32_MC2_ADDR

2

0x0-0xF 0x0425 IA32_MC9_STATUS 0x0-0xF 0x0290 IA32_MC16_CTL2

0x0-0xF 0x040B IA32_MC2_MISC

2

0x0-0xF 0x0426 IA32_MC9_ADDR 0x0-0xF 0x0441 IA32_MC16_STATUS

0x0-0xF 0x040C IA32_MC3_CTL 0x0-0xF 0x0427 IA32_MC9_MISC 0x0-0xF 0x0442 IA32_MC16_ADDR

0x0-0xF 0x0283 IA32_MC3_CTL2 0x0-0xF 0x0428 IA32_MC10_CTL 0x0-0xF 0x0443 IA32_MC16_MISC

0x0-0xF 0x040D IA32_MC3_STATUS 0x0-0xF 0x028A IA32_MC10_CTL2 0x0-0xF 0x0444 IA32_MC17_CTL

0x0-0xF 0x040E IA32_MC3_ADDR 0x0-0xF 0x0429 IA32_MC10_STATUS 0x0-0xF 0x0291 IA32_MC17_CTL2

0x0-0xF 0x040F IA32_MC3_MISC 0x0-0xF 0x042A IA32_MC10_ADDR 0x0-0xF 0x0445 IA32_MC17_STATUS

0x0-0xF 0x0410 IA32_MC4_CTL 0x0-0xF 0x042B IA32_MC10_MISC 0x0-0xF 0x0446 IA32_MC17_ADDR

0x0-0xF 0x0284 IA32_MC4_CTL2 0x0-0xF 0x042C IA32_MC11_CTL 0x0-0xF 0x0447 IA32_MC17_MISC

0x0-0xF 0x0411 IA32_MC4_STATUS 0x0-0xF 0x028B IA32_MC11_CTL2 0x0-0xF 0x0448 IA32_MC18_CTL

0x0-0xF 0x0412 IA32_MC4_ADDR

2

0x0-0xF 0x042D IA32_MC11_STATUS 0x0-0xF 0x0292 IA32_MC18_CTL2

0x0-0xF 0x0413 IA32_MC4_MISC

2

0x0-0xF 0x042E IA32_MC11_ADDR 0x0-0xF 0x0449 IA32_MC18_STATUS

0x0-0xF 0x0414 IA32_MC5_CTL 0x0-0xF 0x042F IA32_MC11_MISC 0x0-0xF 0x044A IA32_MC18_ADDR

0x0-0xF 0x0285 IA32_MC5_CTL2 0x0-0xF 0x0430 IA32_MC12_CTL 0x0-0xF 0x044B IA32_MC18_MISC

0x0-0xF 0x0415 IA32_MC5_STATUS 0x0-0xF 0x028C IA32_MC12_CTL2 0x0-0xF 0x044C IA32_MC19_CTL

0x0-0xF 0x0416 IA32_MC5_ADDR 0x0-0xF 0x0431 IA32_MC12_STATUS 0x0-0xF 0x0293 IA32_MC19_CTL2

0x0-0xF 0x0417 IA32_MC5_MISC 0x0-0xF 0x0432 IA32_MC12_ADDR 0x0-0xF 0x044D IA32_MC19_STATUS

0x0-0xF 0x0418 IA32_MC6_CTL 0x0-0xF 0x0433 IA32_MC12_MISC 0x0-0xF 0x044E IA32_MC19_ADDR

0x0-0xF 0x0286 IA32_MC6_CTL2 0x0-0xF 0x0434 IA32_MC13_CTL 0x0-0xF 0x0179 IA32_MCG_CAP

0x0-0xF 0x0419 IA32_MC6_STATUS 0x0-0xF 0x028D IA32_MC13_CTL2 0x0-0xF 0x017A IA32_MCG_STATUS

0x0-0xF 0x041A IA32_MC6_ADDR 0x0-0xF 0x0435 IA32_MC13_STATUS 0x0-0xF 0x0178 IA32_MCG_CONTAIN

Table 2-11. RdIAMSR() Services Summary (Sheet 2 of 2)

Process

or ID

(byte)

MSR

Address

(dword)

Meaning

Process

or ID

(byte)

MSR

Address

(dword)

Meaning

Proces

sor ID

(byte)

MSR

Address

(dword)

Meaning