Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 89

Datasheet Volume One

Power Management

4.1.4 DMI2/PCI Express Link States

Note: L1 is only supported when the DMI2/PCI Express* port is operating as a PCI Express* port.

4.1.5 Intel QuickPath Interconnect States

4.1.6 G, S, and C State Combinations

Self-Refresh CKE de-asserted. In this mode, no transactions are executed and the system

memory consumes the minimum possible power. Self refresh modes apply to

all memory channels for the processor.

• IO-MDLL Off: Option that sets the IO master DLL off when self refresh

occurs.

• PLL Off: Option that sets the PLL off when self refresh occurs.

In addition, the register component found on registered DIMMs (RDIMMs) is

complemented with the following power down states:

— Clock Stopped Power Down with IBT-On

— Clock Stopped Power Down with IBT-Off

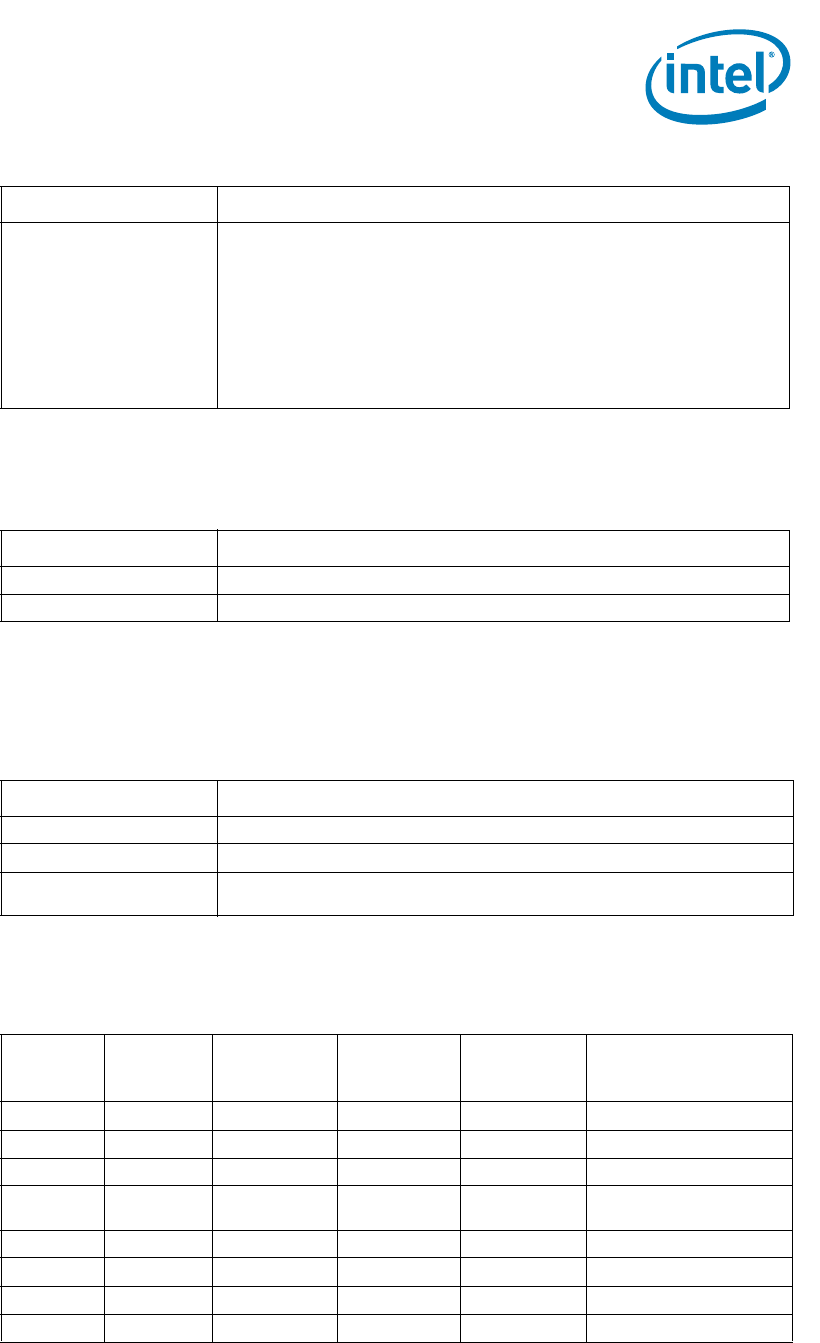

Table 4-5. DMI2/PCI Express* Link States

State Description

L0 Full on – Active transfer state.

L1 Lowest Active State Power Management (ASPM) - Longer exit latency.

Table 4-4. System Memory Power States (Sheet 2 of 2)

State Description

Table 4-6. Intel QPI States

State Description

L0 Link on. This is the power on active working state,

L0p A lower power state from L0 that reduces the link from full width to half width

L1 A low power state with longer latency and lower power than L0s and is

activated in conjunction with package C-states below C0.

Table 4-7. G, S and C State Combinations

Global (G)

State

Sleep

(S) State

Processor

Core

(C) State

Processor

State

System

Clocks

Description

G0 S0 C0 Full On On Full On

G0 S0 C1/C1E Auto-Halt On Auto-Halt

G0 S0 C3 Deep Sleep On Deep Sleep

G0 S0 C6/C7 Deep Power

Down

On Deep Power Down

G1 S3 Power off Off, except RTC Suspend to RAM

G1 S4 Power off Off, except RTC Suspend to Disk

G2 S5 Power off Off, except RTC Soft Off

G3 N/A Power off Power off Hard off