Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 41

Datasheet Volume One

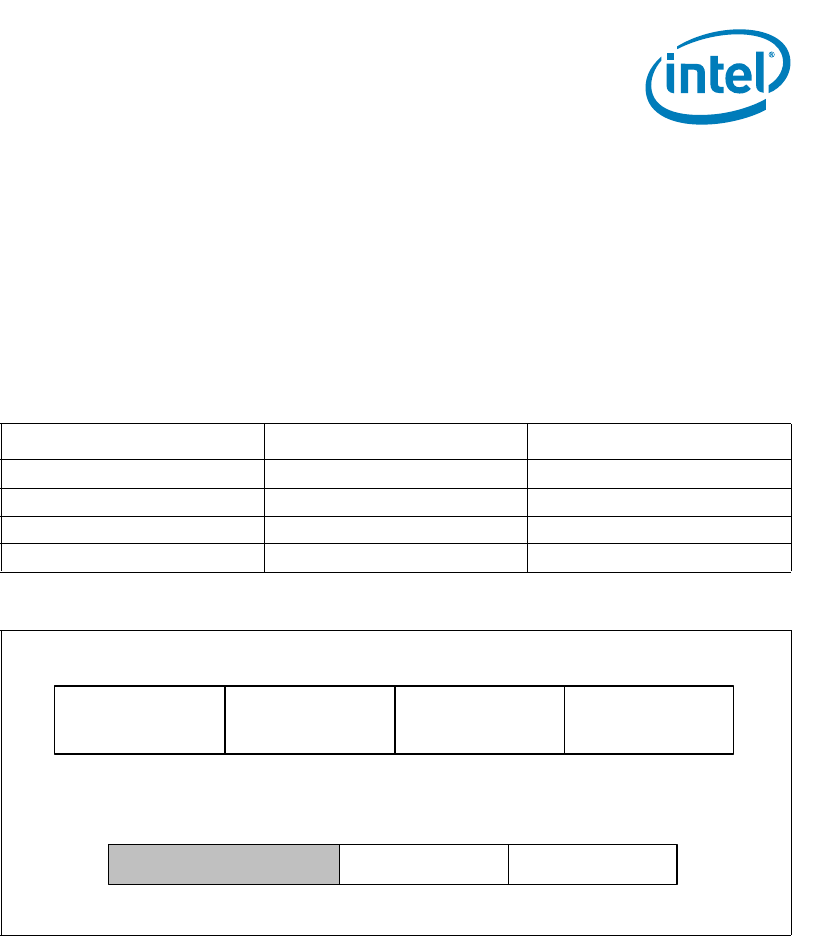

2.5.2.6.3 DRAM Rank Temperature Write

This feature allows the PECI host to program into the processor, the temperature for all

the ranks within a DIMM up to a maximum of four ranks as shown in Figure 2-13. The

DIMM index and Channel index are specified through the parameter field as shown in

Table 2-7. This write is relevant in platforms that do not have on-die or on-board

DIMM thermal sensors to provide memory temperature information or if the processor

does not have direct access to the DIMM thermal sensors. This temperature

information is used by the processor in conjunction with the activity-based DRAM

temperature estimations.

2.5.2.6.4 DIMM Temperature Read

This feature allows the PECI host to read the temperature of all the DIMMs within a

channel up to a maximum of three DIMMs. This read is not limited to platforms using a

particular memory temperature source or temperature estimation method. For

platforms using DRAM thermal estimation, the PCU will provide the estimated

temperatures. Otherwise, the data represents the latest DIMM temperature provided

by the TSOD or on-board DIMM sensor and requires that CLTT (closed loop throttling

mode) be enabled and OLTT (open loop throttling mode) be disabled. Refer to Table 2-7

for channel index encodings.

Table 2-7. Channel & DIMM Index Decoding

Index Encoding Physical Channel# Physical DIMM#

000 0 0

001 1 1

010 2 2

011 3 Reserved

Figure 2-13. DRAM Rank Temperature Write Data

015 7

Rank Temperature Data

Rank# 3

Absolute Temp

(in Degrees C)

Rank# 2

Absolute Temp

(in Degrees C)

Rank# 1

Absolute Temp

(in Degrees C)

Rank# 0

Absolute Temp

(in Degrees C)

816232431

15

2

Parameter format

Reserved DIMM Index

6

Channel Index

5 3 0