DDR3THIN-MN-XXX 31 Doc. Rev. 1.11

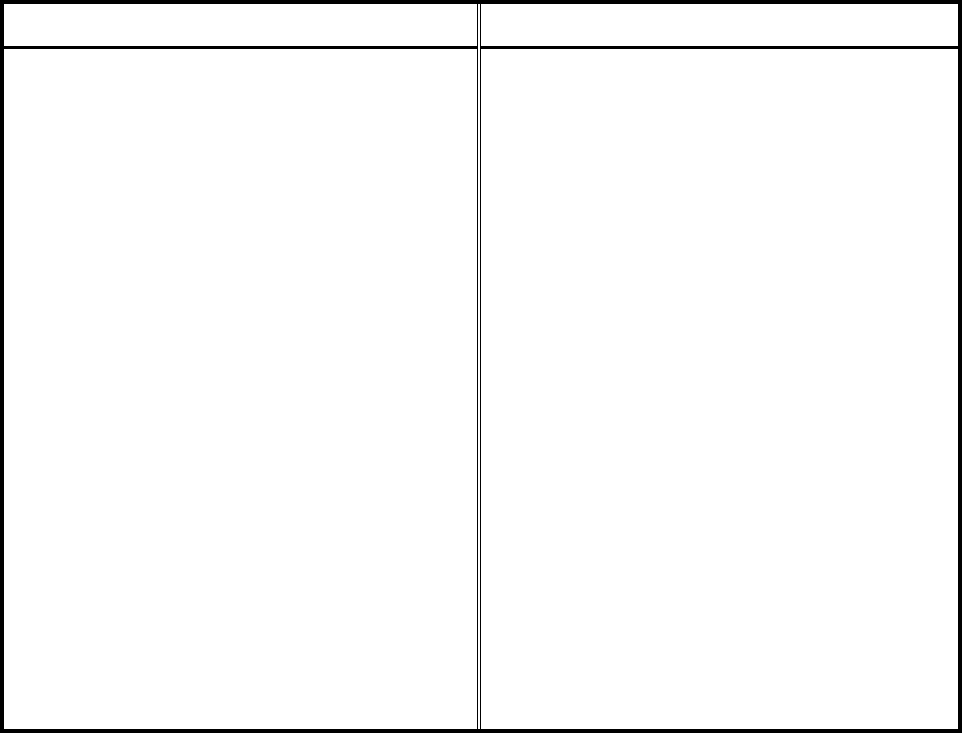

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdA_DatHi RD_A_DQ63 234 S_A2:0 RdA_DatLo RD_A_DQ31 156 M_A0:6

(Hex) RD_A_DQ62 233 S_A2:1 (Hex) RD_A_DQ30 155 M_A0:3

RD_A_DQ61 228 S_A2:5 RD_A_DQ29 150 S_C2:0

RD_A_DQ60 227 S_CK0 RD_A_DQ28 149 S_C2:1

RD_A_DQ59 115 S_A2:2 RD_A_DQ27 37 M_A0:4

RD_A_DQ58 114 S_A2:3 RD_A_DQ26 36 M_A0:1

RD_A_DQ57 109 S_A2:7 RD_A_DQ25 31 S_C2:2

RD_A_DQ56 108 S_A3:0 RD_A_DQ24 30 S_C2:3

RD_A_DQ55 225 S_A3:2 RD_A_DQ23 147 S_C2:4

RD_A_DQ54 224 S_A3:3 RD_A_DQ22 146 S_C2:5

RD_A_DQ53 219 S_A3:7 RD_A_DQ21 141 S_C3:2

RD_A_DQ52 218 S_A1:5 RD_A_DQ20 140 S_C3:3

RD_A_DQ51 106 S_A3:1 RD_A_DQ19 28 S_C2:6

RD_A_DQ50 105 S_A3:4 RD_A_DQ18 27 S_C2:7

RD_A_DQ49 100 S_A1:7 RD_A_DQ17 22 S_C3:1

RD_A_DQ48 99 S_A1:6 RD_A_DQ16 21 S_C3:4

RD_A_DQ47 216 S_A1:4 RD_A_DQ15 138 S_C3:6

RD_A_DQ46 215 S_A1:1 RD_A_DQ14 137 S_C3:7

RD_A_DQ45 210 S_A0:7 RD_A_DQ13 132 S_E3:4

RD_A_DQ44 209 S_A0:6 RD_A_DQ12 131 S_E3:1

RD_A_DQ43 97 S_A1:3 RD_A_DQ11 19 S_C3:5

RD_A_DQ42 96 S_A1:2 RD_A_DQ10 18 S_E3:7

RD_A_DQ41 91 S_A0:5 RD_A_DQ9 13 S_E3:3

RD_A_DQ40 90 S_A0:4 RD_A_DQ8 12 S_E3:2

RD_A_DQ39 207 S_A0:3 RD_A_DQ7 129 S_E3:0

RD_A_DQ38 206 S_A0:2 RD_A_DQ6 128 S_E2:7

RD_A_DQ37 201 M_C2:1 RD_A_DQ5 123 S_E2:3

RD_A_DQ36 200 M_C2:4 RD_A_DQ4 122 S_E2:2

RD_A_DQ35 88 S_A0:1 RD_A_DQ3 10 S_Q3

RD_A_DQ34 87 S_A0:0 RD_A_DQ2 9 S_E2:5

RD_A_DQ33 83 M_C2:6 RD_A_DQ1 4 S_E2:1

RD_A_DQ32 81 M_C2:7 RD_A_DQ0 3 S_E2:0

Table 3 - B_DDR3D_3A (<=1066MT/s Read and Write) TLA Channel Grouping

Notes:

1. All signals on this page are required for accurate post-processing of acquired data

2. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

3. The ‘S’ in front of a TLA channel denotes Slave card #1 of the merged set