2-79

2 Instructions

CP1E CPU Unit Instructions Reference Manual(W483)

Timer and Counter Instructions

2

TIML/TIMLX

Sample program

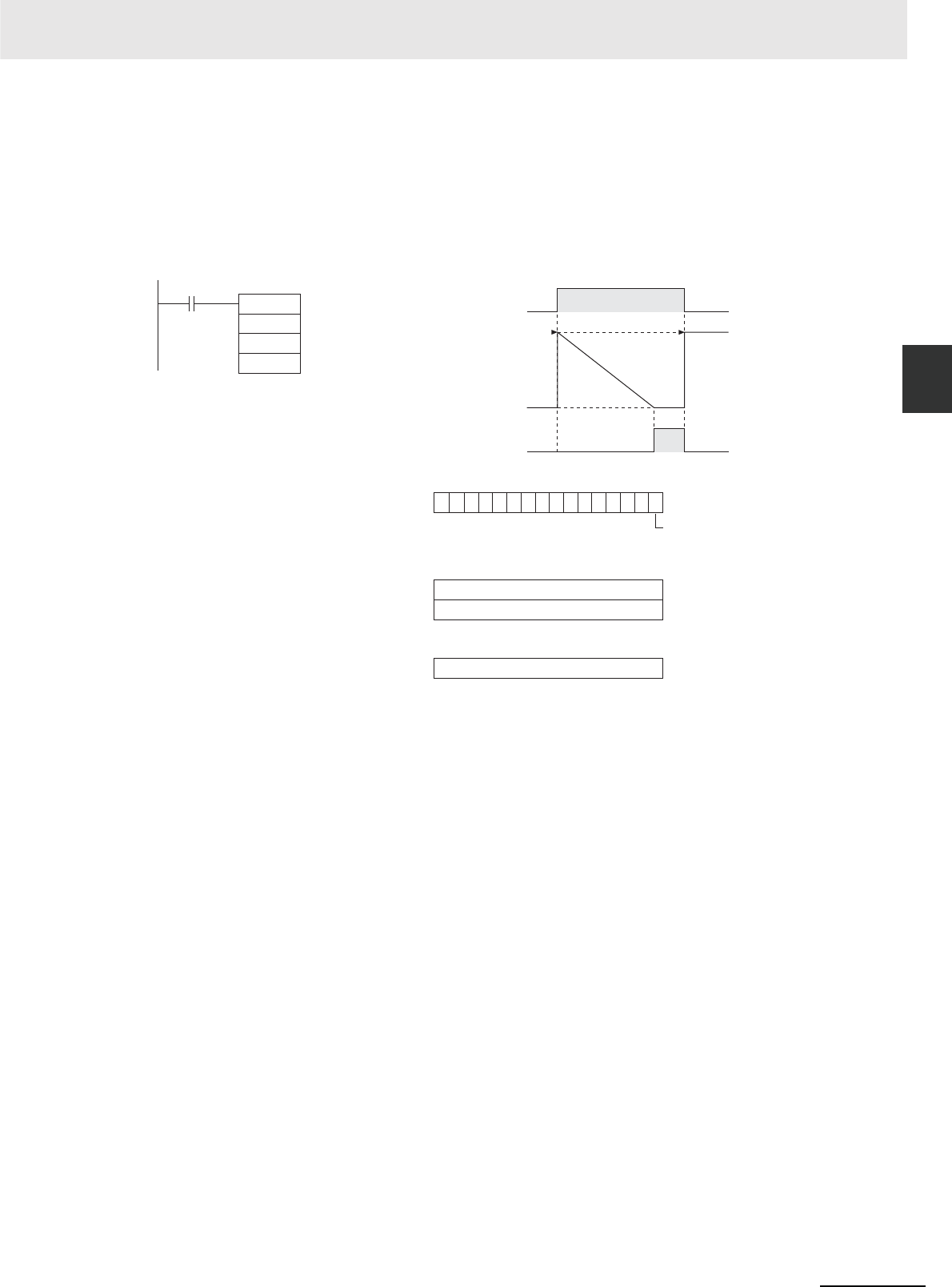

When timer input CIO 0.00 is ON in the following example, the timer PV (in D201 and D200) will be set

to the SV (in D101 and D100) and the PV will begin counting down. The timer Completion Flag (CIO

200.00) will be turned ON when the PV reaches 0.

When CIO 0.00 goes OFF, the timer PV will be reset to the SV and the Completion Flag will be turned

OFF.

TIML

200

D100

D200

0.00

ON

OFF

0

ON

OFF

D1

D2

S

D1:200

0123456789101112131415

D2:D100

D101

015

D200D201

#0010 #0000

(CIO 0200.00)

Timer SV

S: D200 and up

S+1: Content of D201

1000.00

Timer input

Timer PV

(D101 and D100)

Timer Completion

Flag

(CIO 200.00)

Timer SV:

(100,000 decimal= 10,000 s)

Timer’s PV (LSB)

Timer’s PV (MSB)

Timer Completion

Flag