2 Instructions

2-20

CP1E CPU Unit Instructions Reference Manual(W483)

TR

Function

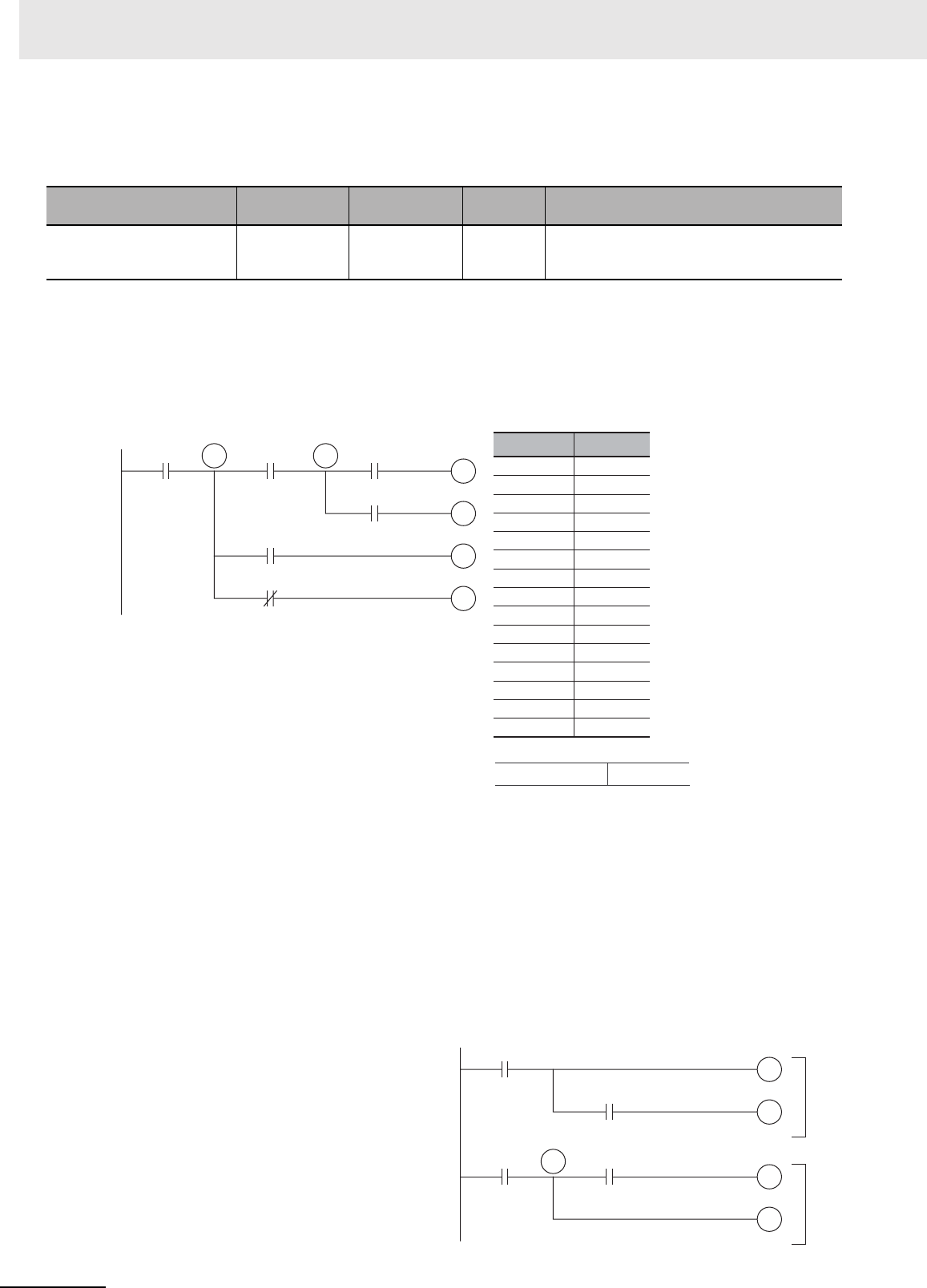

TR bits are used to temporarily retain the ON/OFF status of execution conditions in a program when

programming in mnemonic code. They are not used when programming directly in ladder program form

because the processing is automatically executed by the Peripheral Device. The following diagram

shows a simple application using two TR bits.

Instruction Mnemonic Variations

Function

code

Function

TR Bits TR --- ---

TR bits are used to temporarily retain the ON/OFF

status of execution conditions in a program when

programming in mnemonic code.

Using TR0 to TR15

• TR0 to TR15 are used only with LOAD and

OUTPUT instructions.

• There are no restrictions on the order in

which the bit addresses are used.

• Sometimes it is possible to simplify a pro-

gram by rewriting it so that TR bits are not

required. The following diagram shows one

case in which a TR bit is unnecessary and

one in which a TR bit is required.

In instruction block (1), the ON/OFF status at

point A is the same as for output CIO 100.00,

so AND 0.01 and OUT 100.01 can be coded

without requiring a TR bit. In instruction block

(2), the status of the branching point and that

of output CIO 100.02 are not necessarily the

same, so a TR bit must be used. In this case,

the number of steps in the program could be

reduced by using instruction block (1) in place

of instruction block (2).

LD 0.00

OUT

Coding

TR0

AND 0.01

OUT TR1

AND 0.02

OUT 100.00

LD TR1

AND 0.03

OUT 100.01

LD TR0

AND 0.04

OUT 100.02

LD TR0

AND NOT

100.00

OUT 100.03

Relay Address

TR0 to TR15Temporary Relay

Instruction Operands

0.00 0.01 0.02

0.03

0.04

0.05

100.00

100.01

100.02

100.03

TR0 TR1

A

0.00

0.01

0.02 0.03

(2)

100.00

100.01

100.02

100.03

TR0

(1)