Features and Specifications

2.3.3 External Synchronous DRAM

Rev.1.01

Oct 28, .2008 2-6

REJ10J1351-0101

2

2.3.3 External Synchronous DRAM (SDRAM)

The M3A-HS19 is provided with a 16-MB synchronous DRAM (SDRAM) as an external main memory. The SDRAM is

controlled by the SH7619 on-chip bus state controller. The SDRAM is accessed in 16-bit bus.

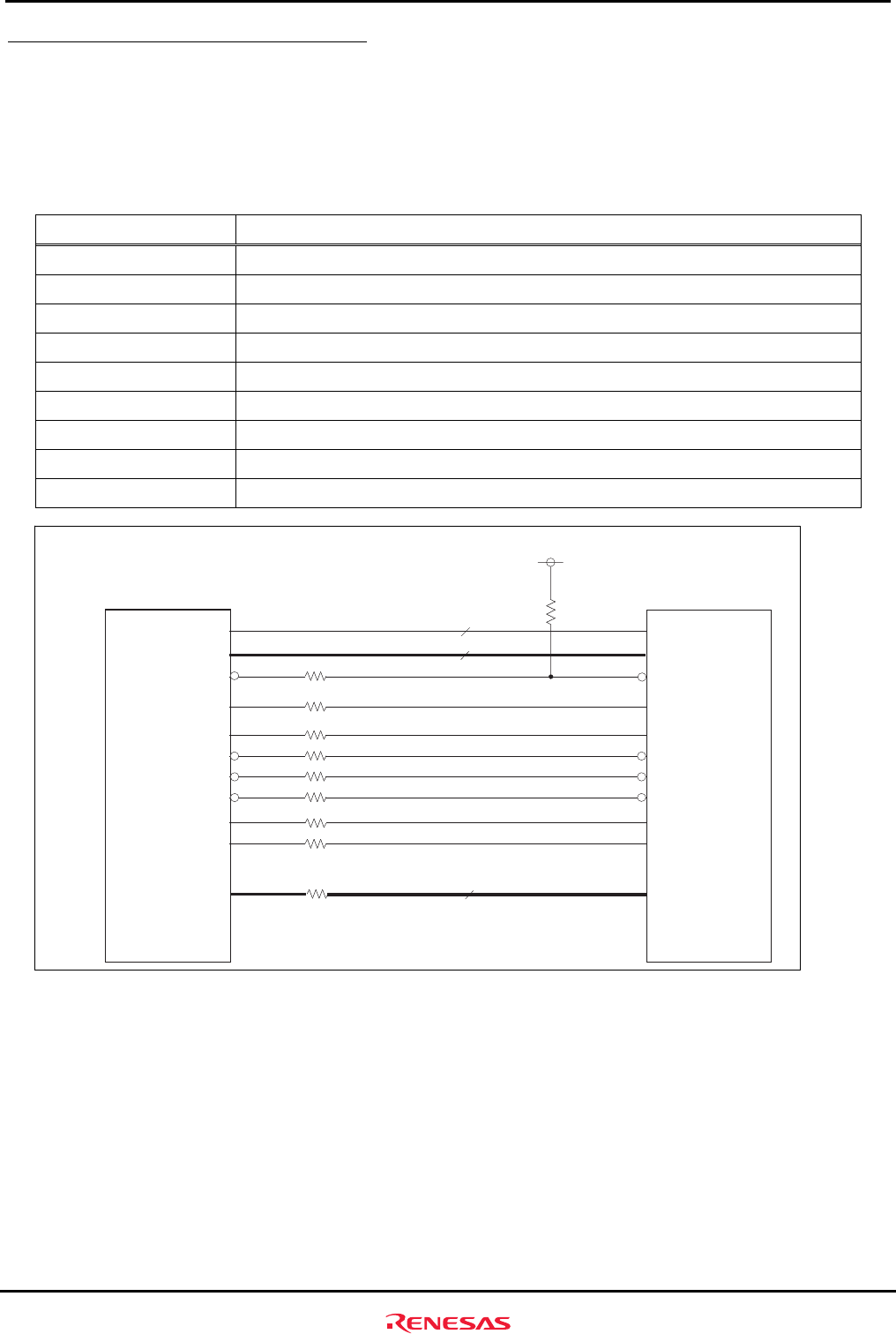

Table 2.3.3 lists SDRAM specifications used on the M3A-HS19, and Figure 2.3.3 shows its block diagram.

Table 2.3.3 SDRAM Specifications

Items Description

Part Number EDS1216AATA-75E

Configuration 16 MB (16-bit bus width) x 1

Capacity 16 MB

Access Time 5.4 ns

CAS Latency 2 (at 62.5 MHz bus clock)

Refresh Interval 4,096 refresh cycles in every 64 ms

Row Address A11- A0

Column Address A8 - A0

Number of Banks 4-banks controlled by BA0, BA1

A12-1

SH7619(U1)

11

CKE

CS3#

RAS#

CKIO

CAS#

RD/WR#

DQMLU

DQMLL

A11-0

EDS1216AATA-75(U3)

(

2 M x 16 bits x 4-bank)

RAS#

CKE

CS#

DQML

DQMU

CLK

CAS#

WE#

3.3V

2

A14-13 BA1-0

D15-0

16

16

DQ15-DQ0

Figure 2.3.3 External SDRAM Block Diagram