ELECTRICAL SPECIFICATION SSD-DXXX(I)-4210 DATA SHEET

SILICONSYSTEMS PROPRIETARY

This document and the information contained within it is confidential and proprietary to SiliconSystems, Inc.

All unauthorized use and/or reproduction is prohibited.

4210D-03DSR PAGE 15 FEBRUARY 2, 2009

3. The delay from the activation of -IORD or -IOWR until the state of IORDY is

first sampled. If IORDY is inactive, then the host waits until IORDY is active

before the PIO cycle can be completed. If the drive is not driving IORDY

negated at t

A

after the activation of -IORD or -IOWR, then t

5

must be met

and t

RD

is not applicable. If the drive is driving IORDY negated at the time t

A

after the activation of -IORD or -IOWR, then t

RD

must be met and t

5

is not

applicable.

4. The symbols t

7

and t

8

apply only to modes 0, 1, and 2. For other modes,

this signal is not valid.

5. IORDY is not supported in this mode.

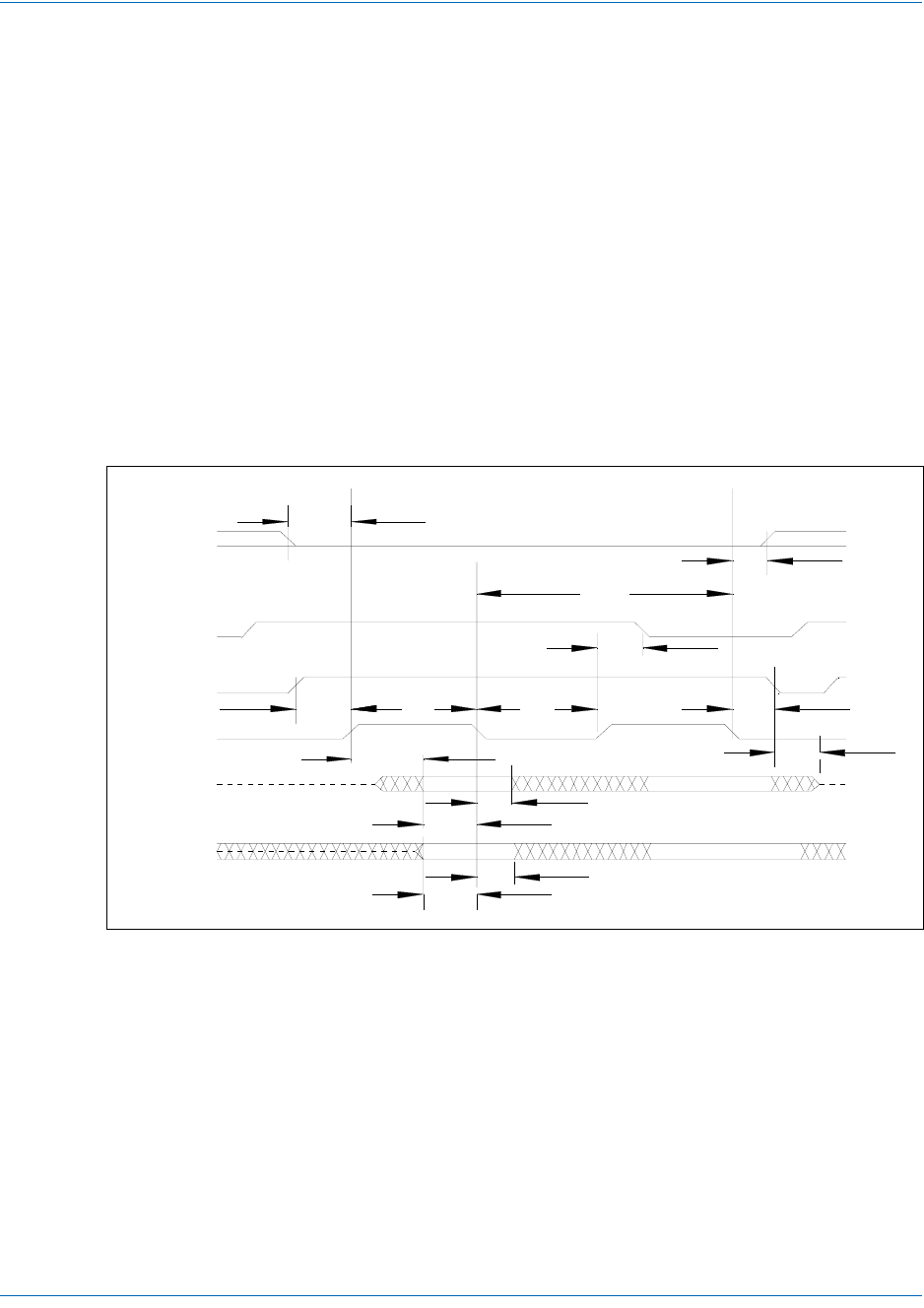

True IDE Multiword DMA Read/Write Access Timing

This function does not apply to SiliconDrive EPs that have DMA disabled.

Figure 5: True IDE Multiword DMA Read/Write Access Timing

Notes:

1. If the drive cannot sustain continuous, minimum cycle time DMA transfers, it

may negate DMARQ within the time specified from the start of a DMA

transfer cycle to suspend the DMA transfers in progress, and reassert the

signal at a later time to continue the DMA operation.

2. This signal may be negated by the host to suspend the DMA transfer in

progress.

Read Data

(D15:D00)

Write Data

(D15:D00)

DMARQ

(See Note 1)

-DMACK

(See Note 2)

-CS0, -CS1

t

t

t

ttt

t

t

t

t

t

t

M

ID

E

G

G

H

F

K

L

O

N

t

J

t

Z

-IORD

-IOWR