Si53xx-RM

Rev. 0.5 147

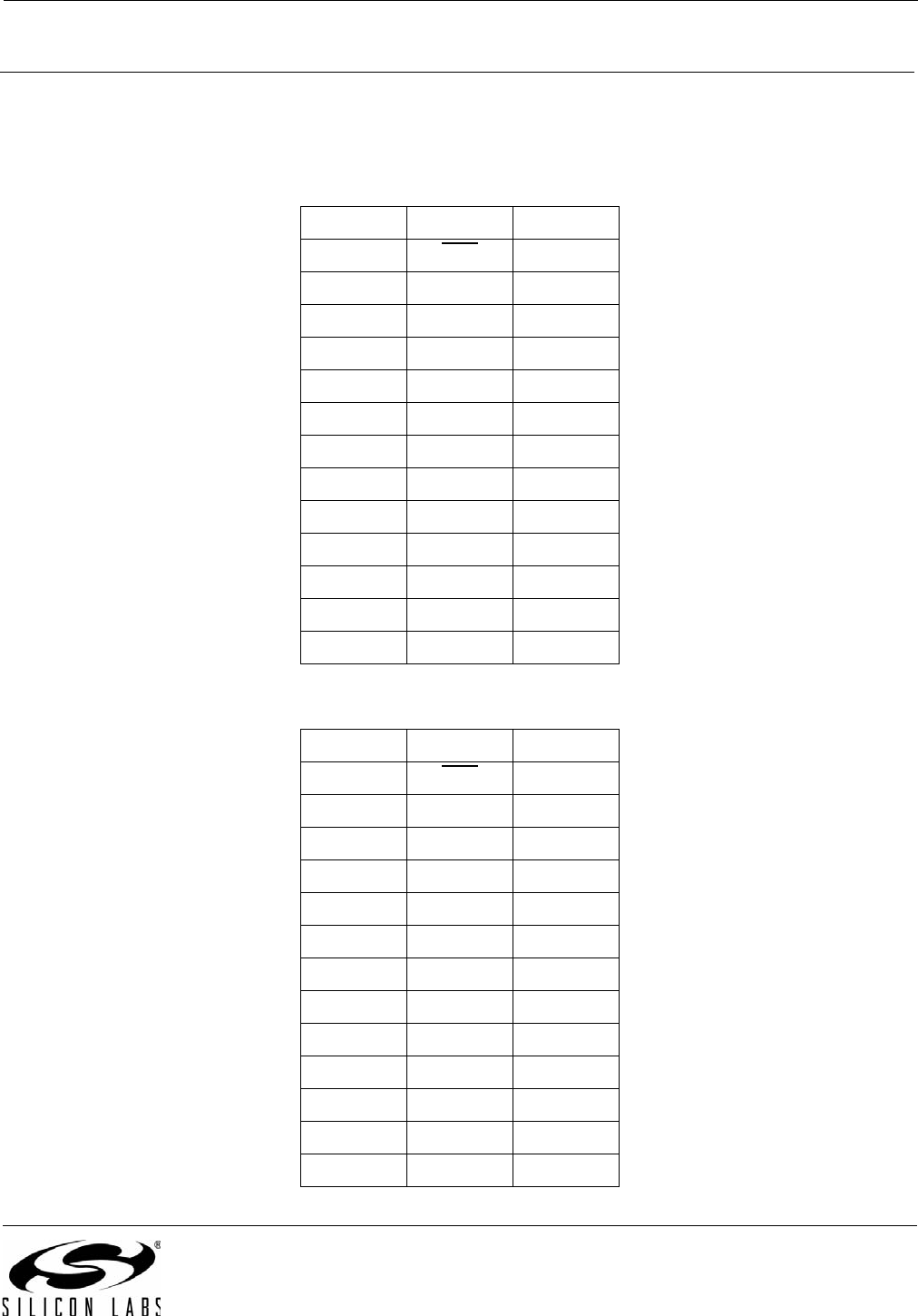

APPENDIX E—INTERNAL PULLUP, PULLDOWN BY PIN

Tables 68–79 show which 2-Level CMOS pins have pullups or pulldowns. Note the value of the pullup/pulldown

resistor is typically 75 k.

Table 68. Si5316 Pullup/Down

Pin # Si5316 Pull?

1

RST

U

11

RATE0 U, D

14

DBL2_BY U, D

15

RATE1 U, D

21

CS U, D

22

BWSEL0 U, D

23

BWSEL1 U, D

24

FRQSEL0 U, D

25

FRQSEL1 U, D

26

CK1DIV U, D

27

CK2DIV U, D

30

SFOUT1 U, D

33

SFOUT0 U, D

Table 69. Si5322 Pullup/Down

Pin # Si5322 Pull?

1RST

U

2FRQTBLU, D

9 AUTOSEL U, D

14 DBL2_BY U, D

21 CS_CA U, D

22 BWSEL0 U, D

23 BWSEL1 U, D

24 FRQSEL0 U, D

25 FRQSEL1 U, D

26 FRQSEL2 U, D

27 FRQSEL3 U, D

30 SFOUT1 U, D

33 SFOUT0 U, D