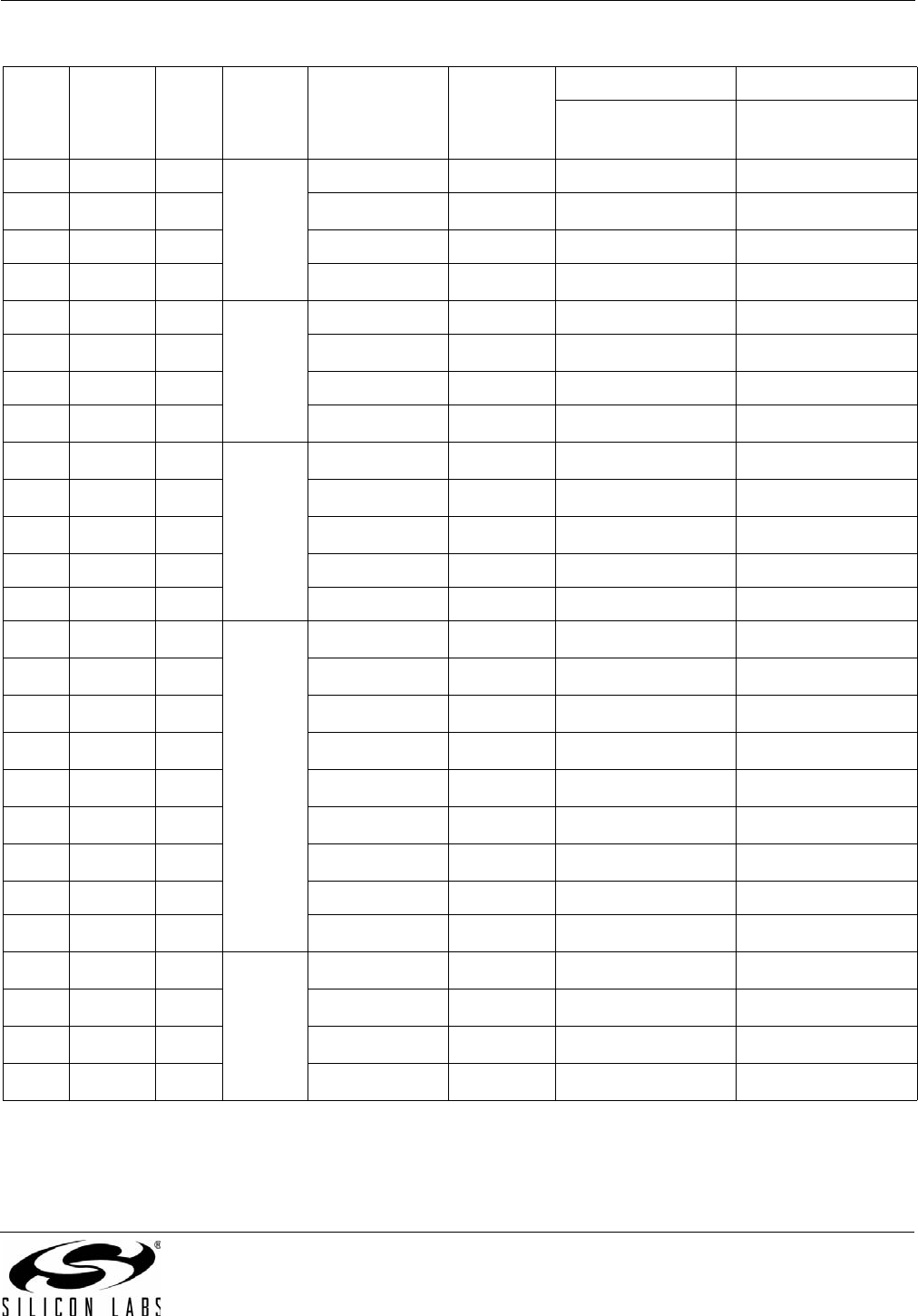

Si53xx-RM

Rev. 0.5 55

56 HLLL 167.33 237/255 155.52 155.52 NA

57 MMHM

1 167.33 167.33 NA

58 HLLM 4 x (237/255) 622.08 622.08 NA

59 MHML

4 669.33 669.33 NA

60 HLLH 168.04 236/255 155.52 155.52 NA

61 MMHM

1 168.04 168.04 NA

62 HLML 4 x (236/255) 622.08 622.08 NA

63 MHML

4 672.16 672.16 NA

64 HLMM

311.04 1 311.04 311.04 0.008

65 HLMH

2 622.08 622.08 0.008

66 HLHL

2 x (255/238) 666.51 666.51 NA

67 HLHM 2 x (255/237) 669.33 669.33 NA

68 HLHH 2 x (255/236) 672.16 672.16 NA

69 HMLL

622.08 1/32 19.44 19.44 0.008

70 HMLM

1/16 38.88 38.88 0.008

71 HMLH

1/8 77.76 77.76 0.008

72 HMML

1/4 155.52 155.52 0.008

73 HMMM

1/2 311.04 311.04 0.008

74 HMMH

1 622.08 622.08 0.008

75 HMHL

255/238 666.51 666.51 NA

76 HMHM 255/237 669.33 669.33 NA

77 HMHH

255/236 672.16 672.16 NA

78 HHLL

666.51 1/4 x 238/255 155.52 155.52 NA

79 HMML

1/4 166.63 166.63 NA

80 HHLM

238/255 622.08 622.08 NA

81 HMMH

1 666.51 666.51 NA

Table 16. SONET Clock Multiplication Settings (FRQTBL=L) (Continued)

No FRQSEL

[3:0]

WB

f

IN

MHz Mult Factor Nominal

f

OUT

MHz

All Devices Si5366 Only

f

CKOUT5

(MHz)

(CK_CONF = 0)

FS_OUT (MHz)

(CK_CONF = 1)