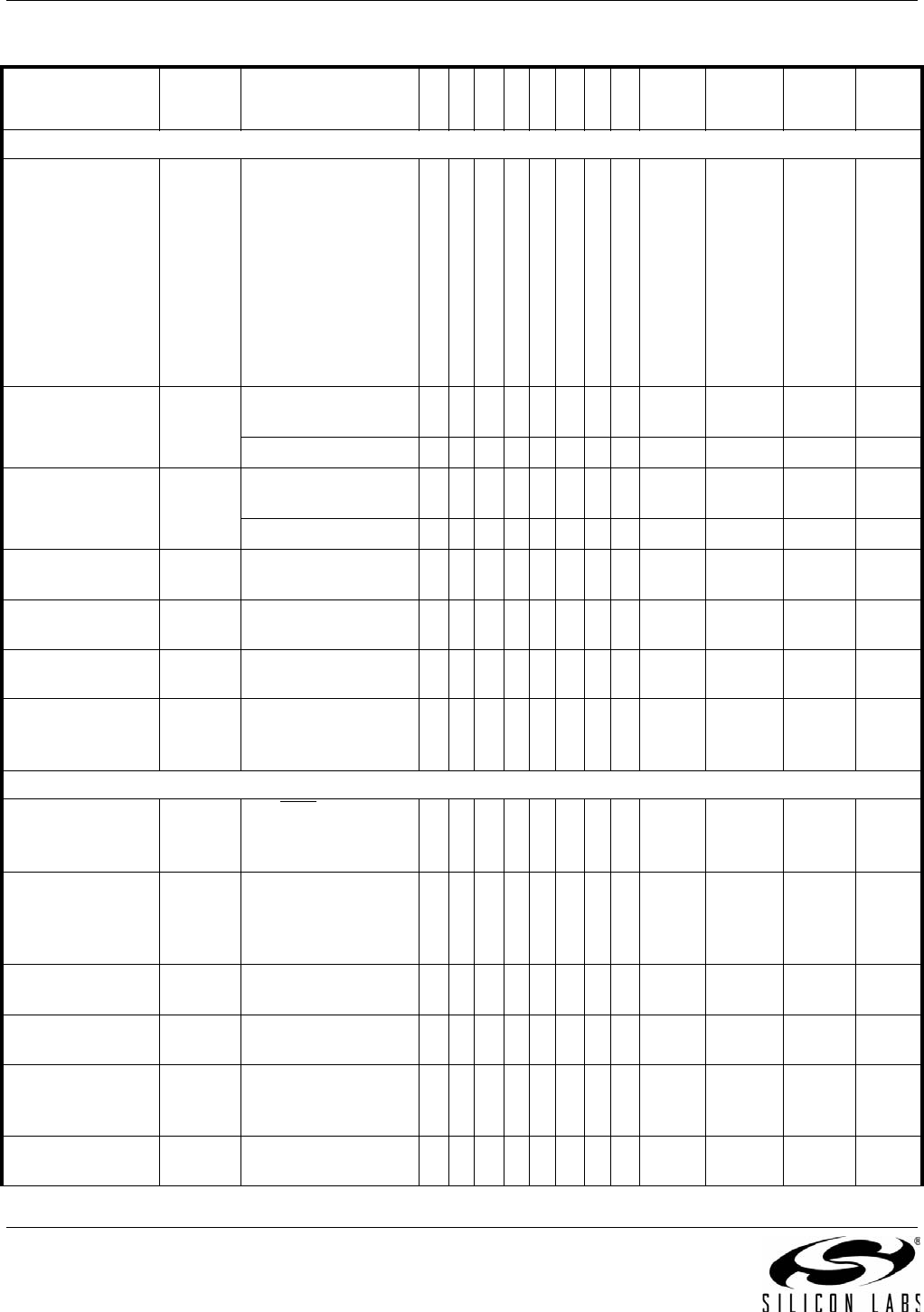

Si53xx-RM

42 Rev. 0.5

Device Skew

Output Clock

Skew,

see Section 7.7.4

t

SKEW

of CKOUT_n to of

CKOUT_m,

CKOUT_n and

CKOUT_m at same

frequency and signal

format

PHASE OFFSET = 0

SQICAL = 1

CKOUT_ALWAYS_O

N=1

——100ps

Coarse Skew

Adjust Resolution

t

PHRES

Using CLAT[7:0]

register

—1/F

VCO

—ps

using INC/DEC pins

—1/F

VCO

—ps

Coarse Skew

Adjust Range

t

PHSRNG

Using CLAT[7:0]

register

– —+

using INC/DEC pins

– —+ s

Fine Skew Adjust

Resolution

t

FPHSRES

using FLAT[14:0]

register

—9 —ps

Fine Skew Adjust

Range

t

FPHSRNG

using FLAT[14:0]

register

–110 — 110 ps

Phase Offset

Resolution

t

OFSTRES

using PHASEOFF-

SETn[7:0] registers

—N1_HS/

f

VCO

—

Phase Offset

Range

t

OFSTRNG

using PHASEOFF-

SETn[7:0] registers

–128 x

t

OF-

STRES

—127 x

t

OF-

STRES

PLL Performance

Lock Time t

LOCKHW

RST with valid

CKIN to LOL;

BW = 100 Hz

—1.2sec

Pin Reset or

Register Reset to

Microprocessor

Access Ready

t

READY

——10ms

Reset to first on

CKOUT

t

START

Valid, stable clock on

CKIN

——1.2sec

Minimum Reset

Pulse Width

t

RSTMIN

1——µs

Lock Time t

LOCKMP

Start of ICAL to of

LOL,

lowest BW setting

— 35 1000 ms

Closed Loop Jitter

Peaking

J

PK

— 0.05 0.1 dB

Table 8. AC Characteristics—All Devices (Continued)

Parameter

Symbol Test Condition

Si5316

Si5322

Si5324

Si5325

Si5365

Si5366

Si5367

Si5368

Min Typ Max Units