SSI

ERP2U Power Supply Design Guide, V2.31

- 31 -

8.2 PWOK (Power OK)

STATUS

Required

PWOK is a power OK signal and will be pulled HIGH by the power supply to indicate that all the outputs are within

the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power

has been removed for a time sufficiently long so that power supply operation is no longer guaranteed, PWOK will

be deasserted to a LOW state. See

Figure 4 for a representation of the timing characteristics of PWOK. The

start of the PWOK delay time shall be inhibited as long as any power supply output is in current limit.

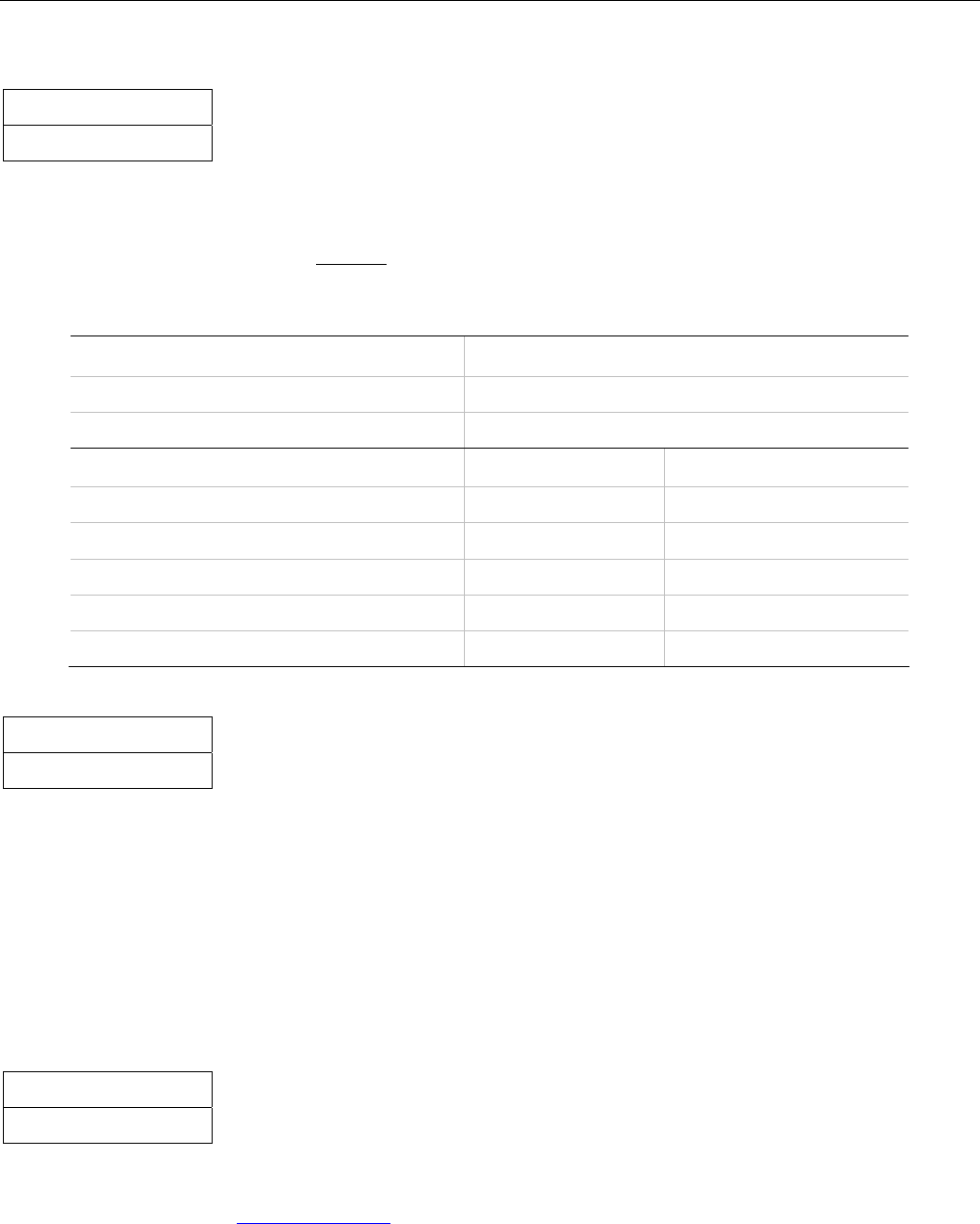

Table 30: PWOK Signal Characteristics

Signal Type

+5V TTL Compatible output signal

PWOK = High

Power OK

PWOK = Low

Power Not OK

MIN MAX

Logic level low voltage, Isink = 4 mA

0 V 0.4 V

Logic level high voltage, Isource=200 μA

2.4 V 5.25 V

PWOK delay: T

pwok_on

200 ms 1000 ms

PWOK rise and fall time

100 μs

Power down delay: T

pwok_off

1 ms

8.3 SMBus Communication

STATUS

Optional

The serial bus communication devices for PSMI and FRU data in the power supply shall be compatible with both

SMBus 2.0 ‘high power’ and I

2

C V

dd

based power and drive. This bus shall operate at 3.3V but tolerant of 5V

signaling. The SMBus pull-ups are located on the motherboard and may be connected to 3.3V or 5V.

Two pins are allocated on the power supply. One pin is the Serial Clock (PSM Clock). The second pin is used for

Serial Data (PSM Data). Both pins are bi-directional and are used to form a serial bus. The device(s) in the

power supply shall be located at an address(s) determined by addressing pins A0 and A1 on the power supply

module. The circuits inside the power supply shall derive their power from the 5VSB bus. Device(s) shall be

powered from the system side of the 5VSB or’ing device. No pull-up resistors shall be on SCL or SDA inside the

power supply. These pull-up resistors should be located external to the power supply.

8.4 Power Supply Management Interface

STATUS

Optional

The PSMI device in the power supply shall derive its power off of the 5VSB output on the system side of the or’ing

device and grounded to ReturnS. It shall be located at an address set by the A0 and A1 pins. Refer to the PSMI

specification posted on the

www.ssiforum.org website for details on the Power Supply Monitoring Interface

requirements. PSMI is a SMBus interface used to communicate power management information to the system.