High Performance Two Port 10/100 Managed Ethernet Switch with 32-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9312 265 Revision 1.4 (08-19-08)

DATASHEET

14.2.9.5 General Purpose Timer Configuration Register (GPT_CFG)

This read/write register configures the LAN9312 General Purpose Timer (GPT). The GPT can be

configured to generate host interrupts at the interval defined in this register. The current value of the

GPT can be monitored via the General Purpose Timer Count Register (GPT_CNT). Refer to Section

12.1, "General Purpose Timer," on page 161 for additional information.

Offset: 08Ch Size: 32 bits

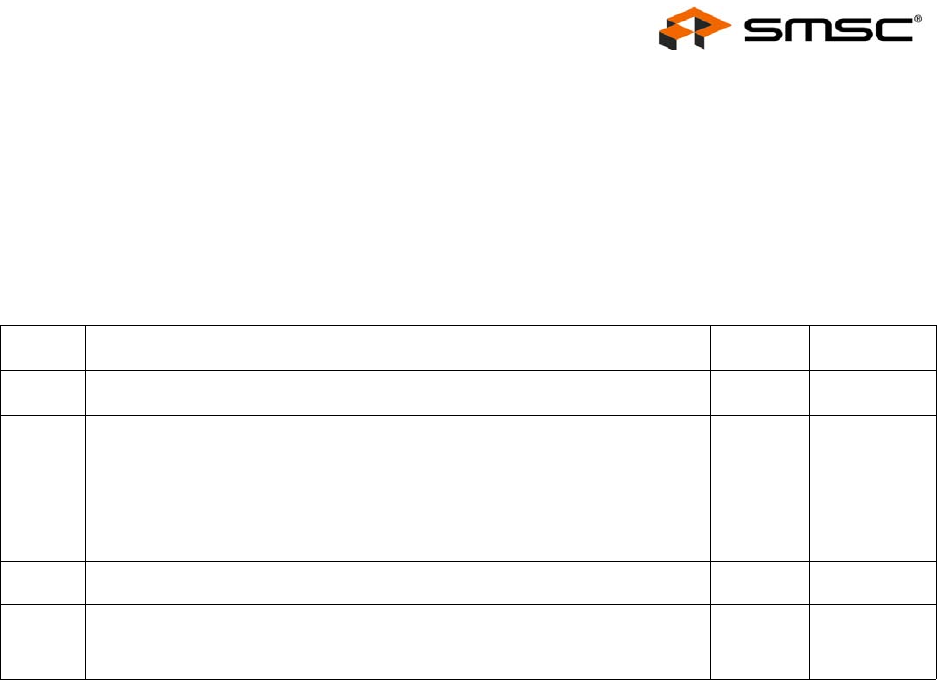

BITS DESCRIPTION TYPE DEFAULT

31:30 RESERVED RO -

29 General Purpose Timer Enable (TIMER_EN)

This bit enables the GPT. When set, the GPT enters the run state. When

cleared, the GPT is halted. On the 1 to 0 transition of this bit, the

GPT_LOAD field of this register will be preset to FFFFh.

0: GPT Disabled

1: GPT Enabled

R/W 0b

28:16

RESERVED RO -

15:0

General Purpose TImer Pre-Load (GPT_LOAD)

This value is pre-loaded into the GPT. This is the starting value of the GPT.

The timer will begin decrementing from this value when enabled.

R/W FFFFh