3-32

X8DTU-LN4F+ Motherboard User's Manual

SP1

JF1

JD1

JWF1

JIPMB2

IPMB1

JP8

VGA2

JPK1

JPW1

JBT1

JPW3

JPW2

J3

J2

J1

JPL2

JPG1

JWD

FAN4

FAN5

FAN3

FAN2

FAN1

FAN6

JBT1

D20

LE11

JL1

JI2C1

JI2C2

JPI2C

USB7

USB4/5

USB2/3

Clear

COMS

JTPM

COM2

UIOP

UID

LAN4

LAN3

LAN2

LAN1

VGA1

COM1

FAN8/CPU1

FAN7/CPU2

CPU2

P1-DIMM2C

P1-DIMM1C

P1-DIMM3C

JTAG of CPLD

SXB1: PCI-E 2.0 x16

SXB3: PCI-E 2.0 x8

SXB2: PCI-E 2.0 x8+x4

P1-DIMM3B

P1-DIMM3A

P1-DIMM1A

P1-DIMM1B

P1-DIMM2B

P1-DIMM2A

CPU1

USB0/1

IPMI_LAN

P2-DIMM2C

P2-DIMM1C

P2-DIMM3C

P2-DIMM3B

P2-DIMM3A

P2-DIMM1A

P2-DIMM1B

P2-DIMM2B

P2-DIMM2A

JPL1

KB/MS

BIOS

FPCTRL

LE1

SATA0~5

LAN1

LAN2

IOH-36D

ICH10R

Intel

Intel

BMC

Winbond

PHY

USB6

T-SGPIO2

T-SGPIO1

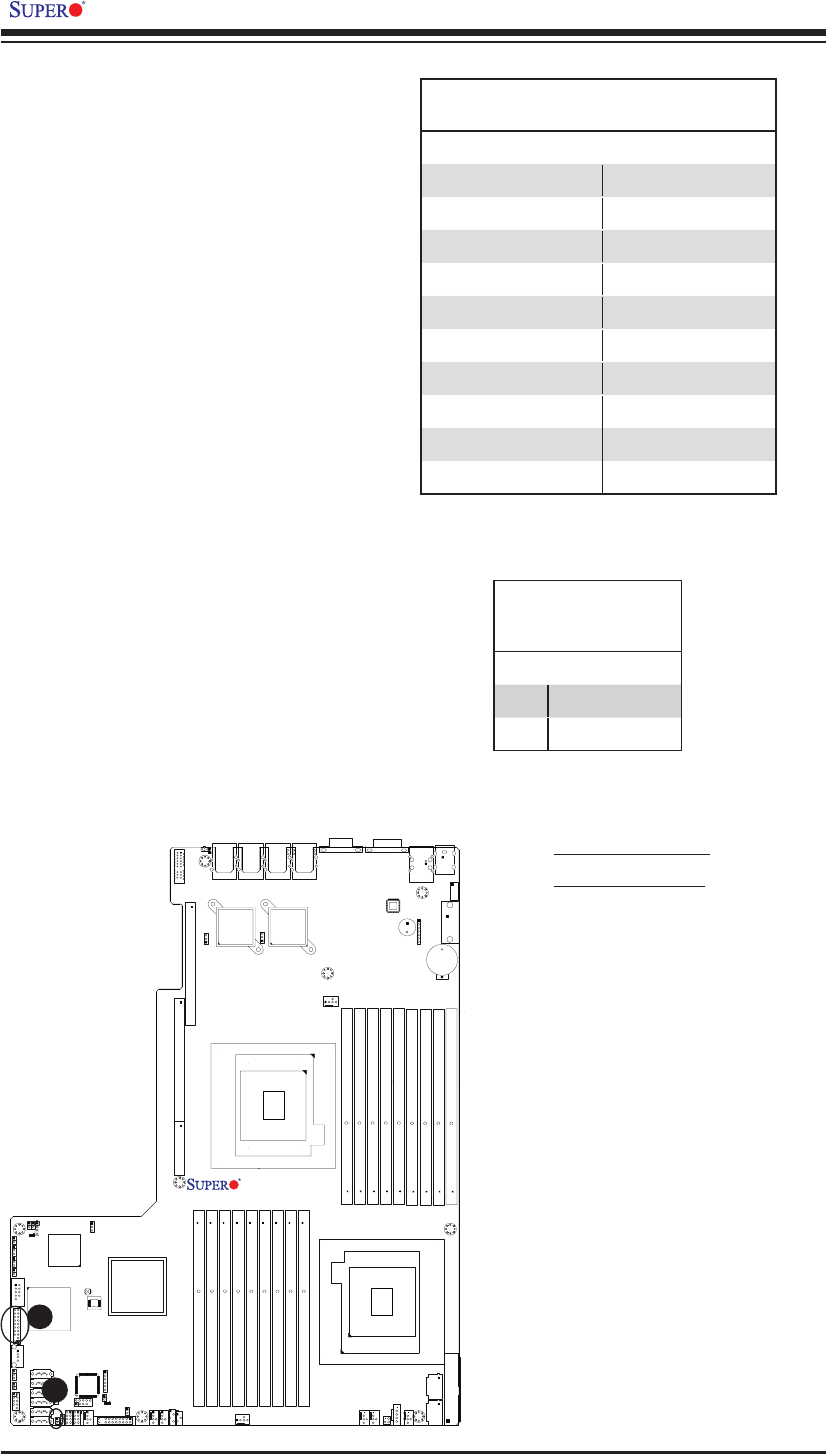

X8DTU-LN4F+

JOH1

WOR1

Rev. 2.0

A

B

A. TPM Connector

B. Wake-On_Ring

Wake-On-Ring

The Wake-On-Ring header is des-

ignated JWOR. This function allows

your computer to waken up when it

receives an incoming call to the mo-

dem while in suspend state. See the

table on the right for pin defi nitions.

You must have a Wake-On-Ring

card and cable to use this feature.

Wake-On-Ring

Pin Defi nitions

(JWOR)

Pin# Defi nition

1 Ground

2 Wake-up

Trusted Platform Module Header

A Trusted Platform Module (TPM)

header (JTPM) is located next to

the COM2 connection. This header

provides TPM support to ensure

data integrity and system security.

Refer to the table on the right for pin

defi nitions.

Trusted Platform Module (TPM) Header

Pin Defi nitions

Pin# Defi nition Pin # Defi nition

1 LPC Clock 2 GND

3 LPC FRAME# 4 Key

5 LPC Reset# 6 +5V (X)

7 LAD3 8 LAD2

9 +3.3V 10 LAD1

11 LAD0 12 GND

13 SCL 14 SDAT

15 +3V_DUAL 16 SERIRQ

17 GND 18 CLKRUN(X)

19 LPCPD# 20 LDRQ#(X)

Notes:

(X)=TPM does not use the signals.

SCL, SDAT are I

2

C bus clock and data.