http://www.tyan.com

100

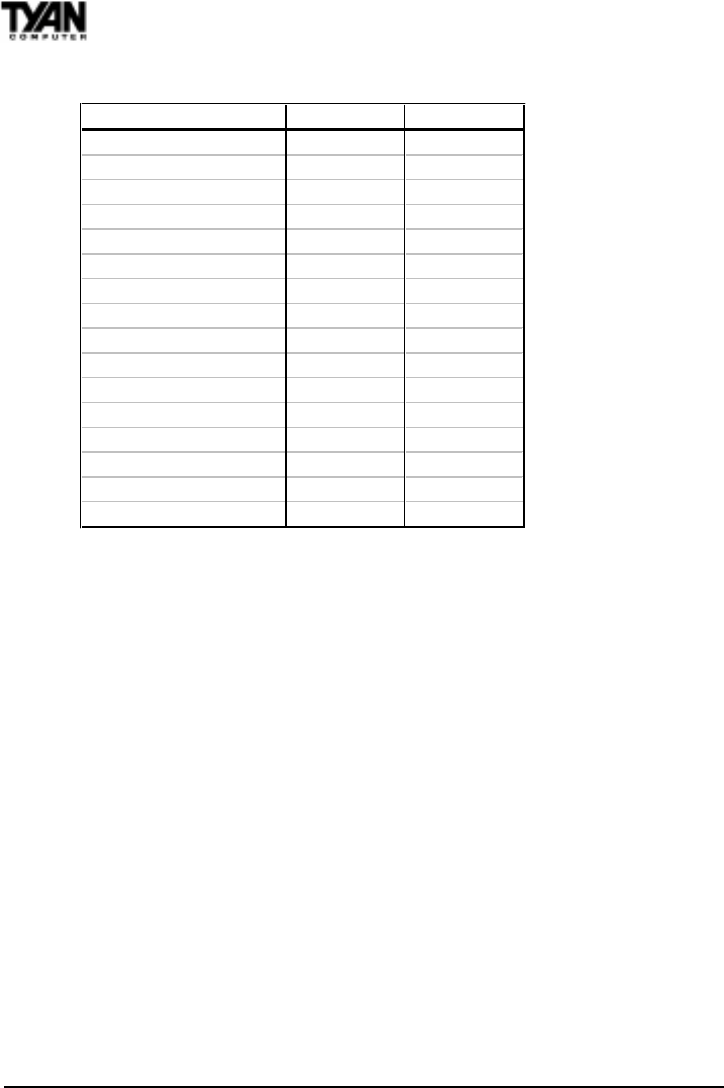

Chipset Features Setup - Default Settings Chart

Bank 0/1, 2/3, 4/5 DRAM Timing

The system board designer must select the proper value for these fields,

according to the specifications of the installed DRAM chips. Turbo mode

reduces CAS access time by 1 clock tick.

SDRAM Cycle Length

This field sets the CAS latency timing.

DRAM Clock

Allows you to set the memory clock speed to either 66MHz or equal to the

CPU clock speed, depending on your memory speed.

Memory Hole

This option specifies the location of an area of memory that cannot be

addressed on the ISA bus. The settings are Disabled, 512KB-64KB, or 15MB-

16MB.

Read Around Write

Increases memory throughput.

Setting Option BIOS Default Setup Default

Bank 0/1 DRAM Timing SDRAM 10ns SDRAM 10ns

Bank 2/3 DRAM Timing SDRAM 10ns SDRAM 10ns

Bank 4/5 DRAM Timing SDRAM 10ns SDRAM 10ns

SDRAM Cycle Length 3 3

DRAM Clock Host CLK Host CLK - 33m

Memory Hole Disabled Disabled

Read Around Write Disabled Disabled

Concurrent PCI/Host Disabled Disabled

System BIOS Cacheable Disabled Disabled

Video RAM Cacheable Disabled Disabled

AGP Aperture Size 64M 64M

AGP-2x Mode Enabled Enabled

OnChip USB Enabled Enabled

USB Keyboard support Disabled Disabled

Auto Detect DIMM/PC2 CLK Enabled Enabled

*HW Monitoring Optional

BIOS 2

Award BIOS Configuration