60 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Chapter 2: MicroBlaze Signal Interface Description

R

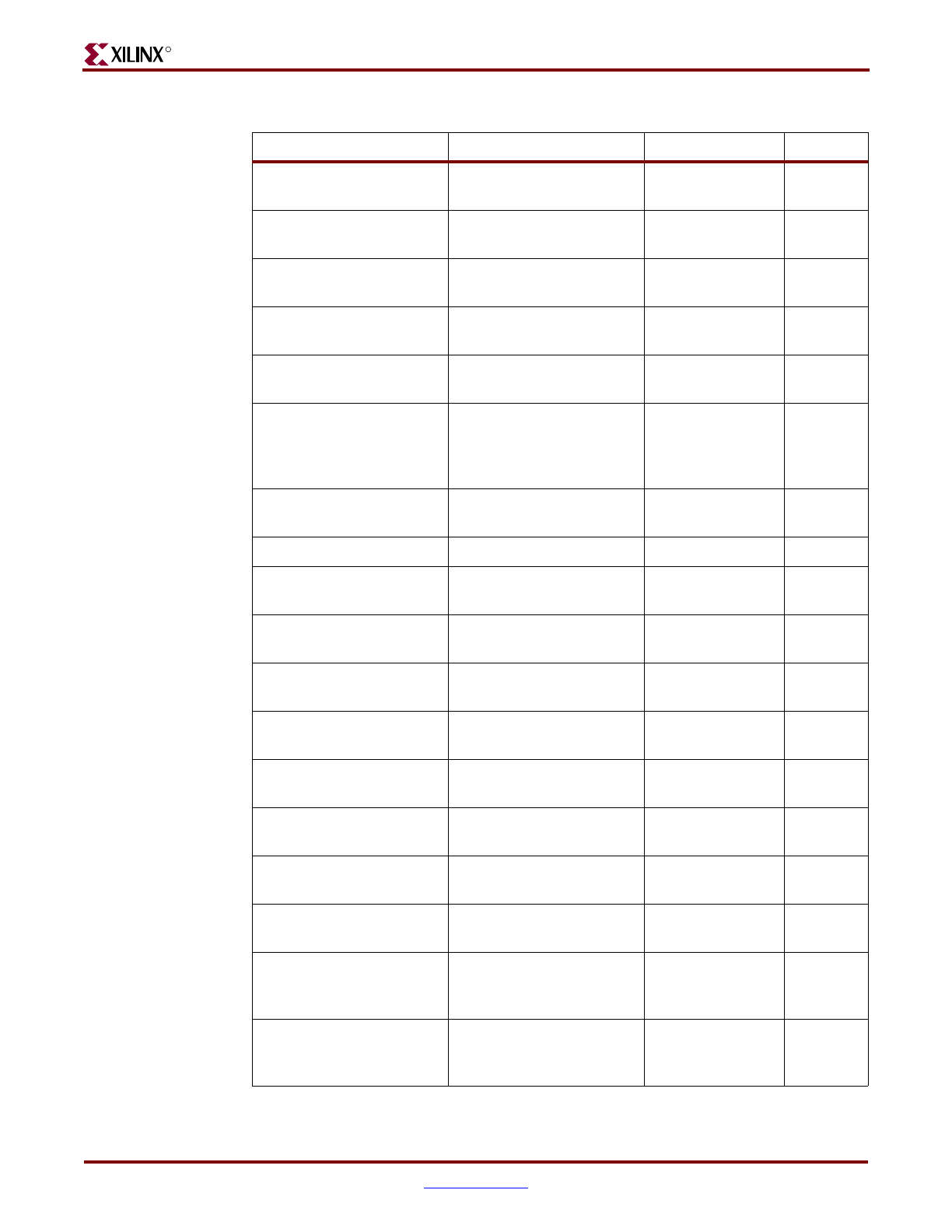

Trace_Reg_Write

1

Instruction writes to the

register file

std_logic output

Trace_Reg_Addr

1

Destination register

address

std_logic_vector

(0 to 4)

output

Trace_MSR_Reg

1

Machine status register std_logic_vector

(0 to10)

output

Trace_New_Reg_Value

1

Destination register

update value

std_logic_vector

(0 to 31)

output

Trace_Exception_Taken

1

Instruction result in taken

exception.

std_logic output

Trace_Exception_Kind

1

Exception type. The

description for the

exception type is

documented in Table 2-11

std_logic_vector

(0 to 3)

output

Trace_Jump_Taken

1

Branch instruction

evaluated true i.e taken

std_logic output

Trace_Delay_Slot

1

Instruction is in delay slot std_logic output

Trace_Data_Access

1

Valid D-side memory

access

std_logic output

Trace_Data_Address

1

Address for D-side

memory access

std_logic_vector

(0 to 31)

output

Trace_Data_Write_Value

1

Value for D-side memory

write access

std_logic_vector

(0 to 31)

output

Trace_Data_Byte_Enable

1

Byte enables for D-side

memory access

std_logic_vector

(0 to 3)

output

Trace_Data_Read

1

D-side memory access is a

read

std_logic output

Trace_Data_Write

1

D-side memory access is a

write

std_logic output

Trace_DCache_Req Data memory address is

within D-Cache range

std_logic output

Trace_DCache_Hit Data memory address is

present in D-Cache

std_logic output

Trace_ICache_Req Instruction memory

address is in I-Cache

range

std_logic output

Trace_ICache_Hit Instruction memory

address is present in I-

Cache

std_logic output

Table 2-10: MicroBlaze Trace signals

Signal Name Description VHDL Type Direction