ASUS P5Q Premium 3-25

TPM Enable/Disable Status [No State]

The item is not congurable.

TPM Owner Status [UnOwned]

The item is not congurable

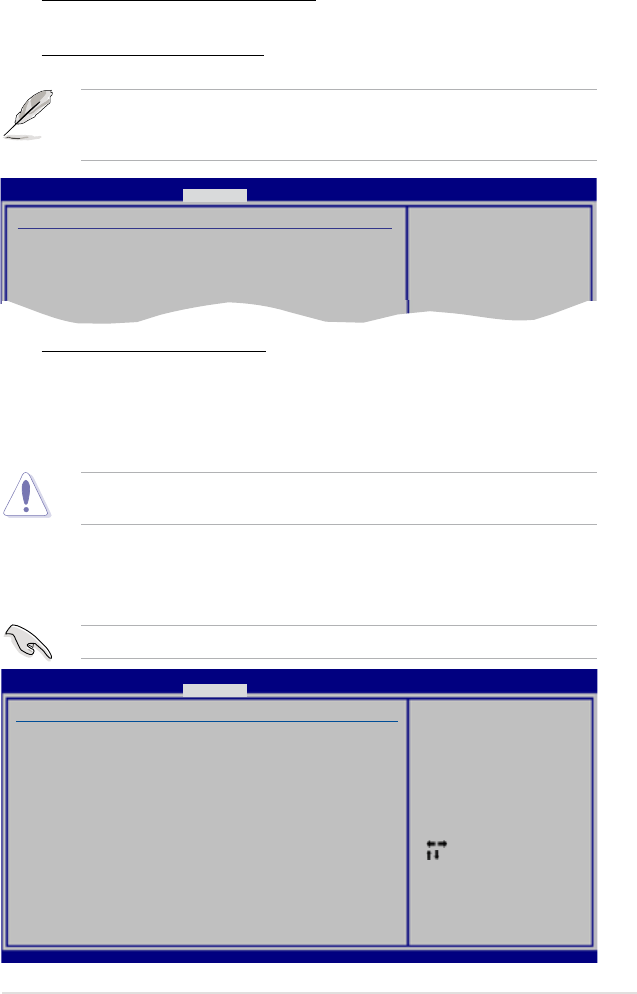

To enable the TPM function, set the Execute TPM Command item to [Enabled]

and then save the change (see 3.9 Exit menu for details). After the system

reboots, the TPM Conguration menu will change into the following one.

TPM Conguration

TCG/TPM [Yes]

Execute TPM Command [Last setting]

TPM Enable/Disable Status [Enabled]

Clearing the TPM [Press Enter]

TPM Owner Status [UnOwned]

Enable (Activate)/

Disable (Deactivate)

Command to TPM

BIOS SETUP UTILITY

Advanced

Clearing the TPM [Press Enter]

Allows you to clear the user information saved in the TPM security chip.

When you press <Enter>, a warning message will appear to ask if you want

to clear the user information in the security chip. Use the left/right arrow key

to select between [Ok] and [Cancel], and then press <Enter> to conrm your

choice.

After you select [Ok] to execute the Clearing the TPM function, the data saved

in the TPM security chip will be cleared and can never be restored.

3.5.2 CPU Conguration

The items in this menu show the CPU-related information that the BIOS

automatically detects.

The items shown in this screen may be different due to the CPU you installed.

Select Screen

Select Item

+- Change Option

F1 General Help

F10 Save and Exit

ESC Exit

v02.61 (C)Copyright 1985-2008, American Megatrends, Inc.

BIOS SETUP UTILITY

Advanced

Congure advanced CPU settings

Manufacturer:Intel

Brand String:Intel(R) Core(TM)2 Duo CPU @ 3.00GHz

Frequency :3.00GHz

FSB Speed :1332 MHz

Cache L1 :64 KB

Cache L2 :4096 KB

Ratio Status: Unlocked (Min:06, Max:09)

Ratio Actual Value:9

CPUID :6F9

CPU Ratio Setting [Auto]

C1E Support [Enabled]

Max CPUID Value Limit [Disabled]

Intel(R) Virtualization Tech [Enabled]

CPU TM function [Enabled]

Execute Disable Bit [Enabled]

Intel(R) SpeedStep(TM) Tech [Enabled]

Intel(R) C-STATE Tech [Disabled]

Sets the ratio between

CPU Core Clock and the

FSB Frequency.

NOTE: If an invalid

ratio is set in CMOS

then actual and

setpoint values may

differ.