Ultra37000 CPLD Family

Document #: 38-03007 Rev. *E Page 18 of 64

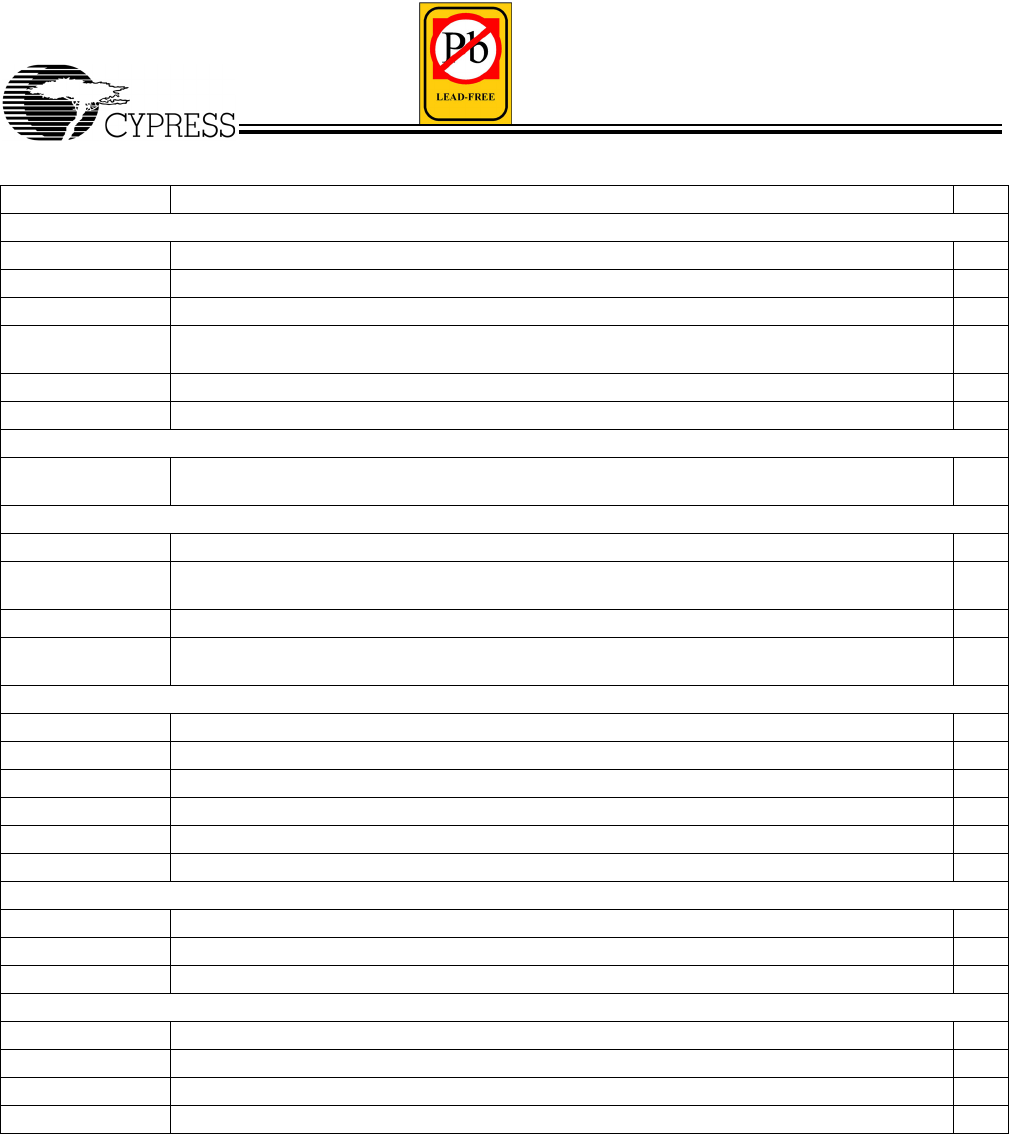

Product Term Clocking Parameters

t

COPT

[13, 14, 15]

Product Term Clock or Latch Enable (PTCLK) to Output ns

t

SPT

Set-Up Time from Input to Product Term Clock or Latch Enable (PTCLK) ns

t

HPT

Register or Latch Data Hold Time ns

t

ISPT

[13]

Set-Up Time for Buried Register used as an Input Register from Input to Product Term Clock or

Latch Enable (PTCLK)

ns

t

IHPT

Buried Register Used as an Input Register or Latch Data Hold Time ns

t

CO2PT

[13, 14, 15]

Product Term Clock or Latch Enable (PTCLK) to Output Delay (Through Logic Array) ns

Pipelined Mode Parameters

t

ICS

[13]

Input Register Synchronous Clock (CLK

0

, CLK

1

, CLK

2

, or CLK

3

) to Output Register Synchronous

Clock (CLK

0

, CLK

1

, CLK

2

, or CLK

3

)

ns

Operating Frequency Parameters

f

MAX1

Maximum Frequency with Internal Feedback (Lesser of 1/t

SCS

, 1/(t

S

+ t

H

), or 1/t

CO

)

[5]

MHz

f

MAX2

Maximum Frequency Data Path in Output Registered/Latched Mode (Lesser of 1/(t

WL

+ t

WH

),

1/(t

S

+t

H

), or 1/t

CO

)

[5]

MHz

f

MAX3

Maximum Frequency with External Feedback (Lesser of 1/(t

CO

+ t

S

) or 1/(t

WL

+ t

WH

)

[5]

MHz

f

MAX4

Maximum Frequency in Pipelined Mode (Lesser of 1/(t

CO

+ t

IS

), 1/t

ICS

, 1/(t

WL

+ t

WH

), 1/(t

IS

+ t

IH

),

or 1/t

SCS

)

[5]

MHz

Reset/Preset Parameters

t

RW

Asynchronous Reset Width

[5]

ns

t

RR

[13]

Asynchronous Reset Recovery Time

[5]

ns

t

RO

[13, 14, 15]

Asynchronous Reset to Output ns

t

PW

Asynchronous Preset Width

[5]

ns

t

PR

[13]

Asynchronous Preset Recovery Time

[5]

ns

t

PO

[13, 14, 15]

Asynchronous Preset to Output ns

User Option Parameters

t

LP

Low Power Adder ns

t

SLEW

Slow Output Slew Rate Adder ns

t

3.3IO

3.3V I/O Mode Timing Adder

[5]

ns

JTAG Timing Parameters

t

S JTAG

Set-up Time from TDI and TMS to TCK

[5]

ns

t

H JTAG

Hold Time on TDI and TMS

[5]

ns

t

CO

JTAG

Falling Edge of TCK to TDO

[5]

ns

f

JTAG

Maximum JTAG Tap Controller Frequency

[5]

ns

Switching Characteristics Over the Operating Range (continued)

[12]

Parameter Description Unit

[+] Feedback