RX − 8564 LC

Page − 20

ETM12E-01

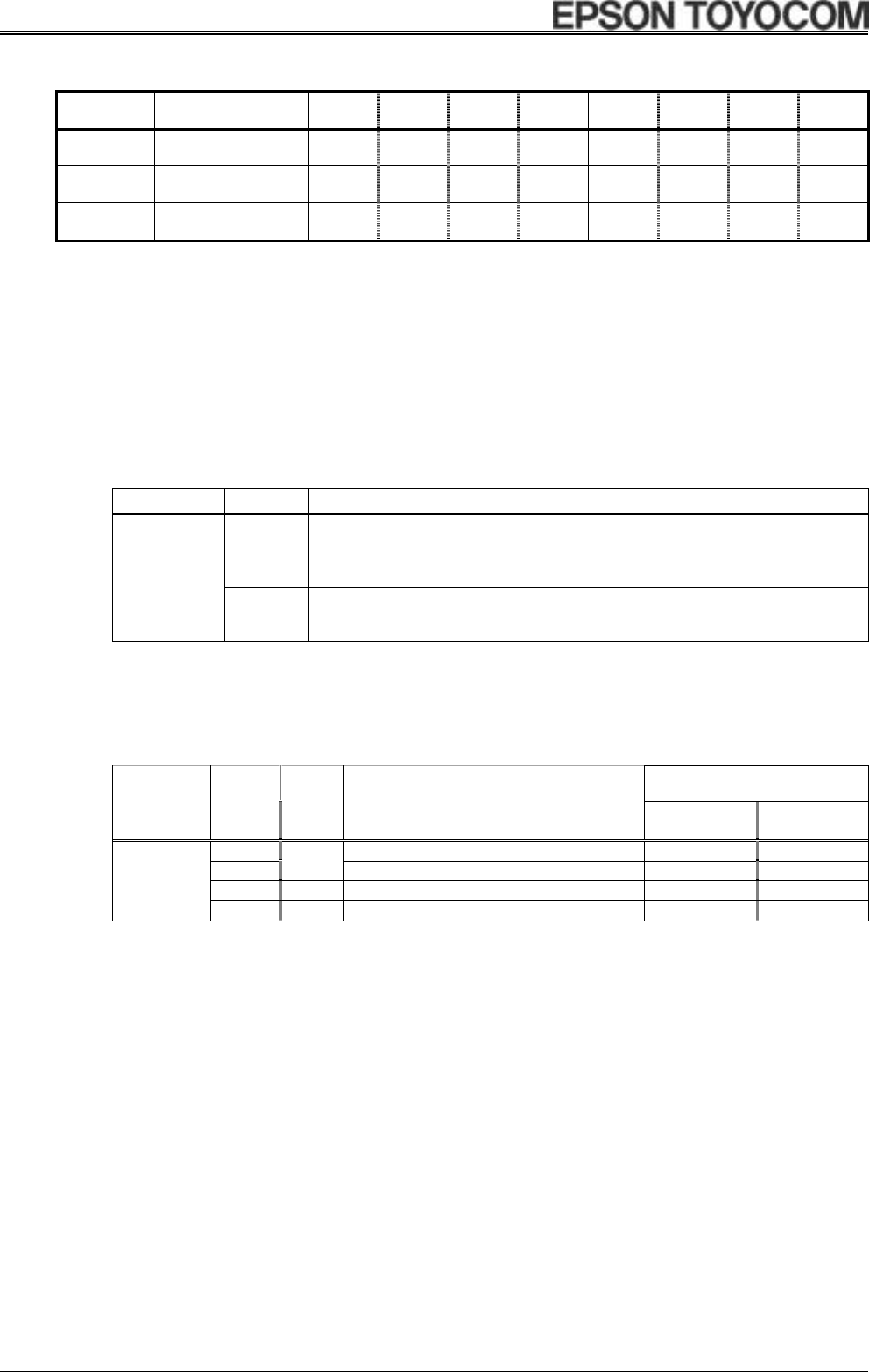

13.2.2. Related registers for function of timer interrupts.

Address [h] Function bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

01 Control 2 0

×

0

TI

/

TP

AF

TF

AIE

TIE

0E Timer control

TE

× × × × ×

TD1 TD0

0F Timer

128 64 32 16 8 4 2 1

∗ Before starting the fixed-cycle timer interrupt function each time, be sure to write a value (preset value/Reg-0F[h])

as the timer's down counter value (when TE = "0").

(Note) Note with caution that the preset value must be set or reset to enable correct operation.

∗ Before entering operation settings, we recommend first clearing the TE bit to "0" and then clearing the TF and TIE

bits to "0" in that order, so that all control-related bits are zero-cleared (= set to operation stop mode) to prevent

hardware interrupts from occurring inadvertently while entering settings.

1) TI / TP bit ( Interrupt Signal Output Mode Select. Interrupt / Periodic )

When a fixed-cycle timer interrupt event occurs, this bit selects whether to end the operation after one

iteration or to repeat the operation.

TI

/

TP

Data Description

0

[Level interrupt mode]

Fixed-cycle timer interrupt function operates one time only

(

∗

)

∗) Another operation can be set via various bit settings.

Write / Read

1

[Repeated interrupt mode]

Fixed-cycle timer interrupt function operates repeatedly

2) TD1, TD0 bits ( Timer countDown interval select 1, 0 )

These bits specify the fixed-cycle timer interrupt function's countdown period (source clock).

Four different periods can be selected via combinations of these two bit values.

/INT auto recovery time tRTN

during repeated interrupt mode

TD1,

TD0

TD1

( bit 1 )

TD0

( bit 0 )

Source clock

Preset value

n = 1

Preset value

1 < n

0 0 4096 Hz

/ 244.14 µs cycle 122 µs 244 µs

0 1 64 Hz

/ 15.625 ms cycle 7.813 ms 15.625 ms

1 0

1 Hz

/ Updated per second

15.625 ms 15.625 ms

W / R

1 1

1/60 Hz

/ Updated per minute

15.625 ms 15.625 ms

∗1) During repeated interrupt mode (TI/TP bit = "1"), the auto recovery time tRTN (when the /INT pin is

switched from low level to Hi-Z) varies according to the source clock and preset value, as shown above.

∗2) The countdown when a 1-Hz source clock has been selected is linked to updating of the internal clock's

seconds setting.

∗ Since the internal clock is linked to updating of the seconds setting, if the timer is started at a clock

time of 0.9 seconds, the first countdown will occur only 0.1 second later. (The second and subsequent

countdowns will occur at the correct time interval.)

∗2) The countdown when a 1/60-Hz source clock has been selected is linked to updating of the internal

clock's minutes setting.

∗ Since the internal clock is linked to updating of the minutes setting, if the timer is started at a clock

time of 50 seconds, the first countdown will occur only 10 seconds later. (The second and subsequent

countdowns will occur at the correct time interval.)