RX − 8564 LC

Page − 26

ETM12E-01

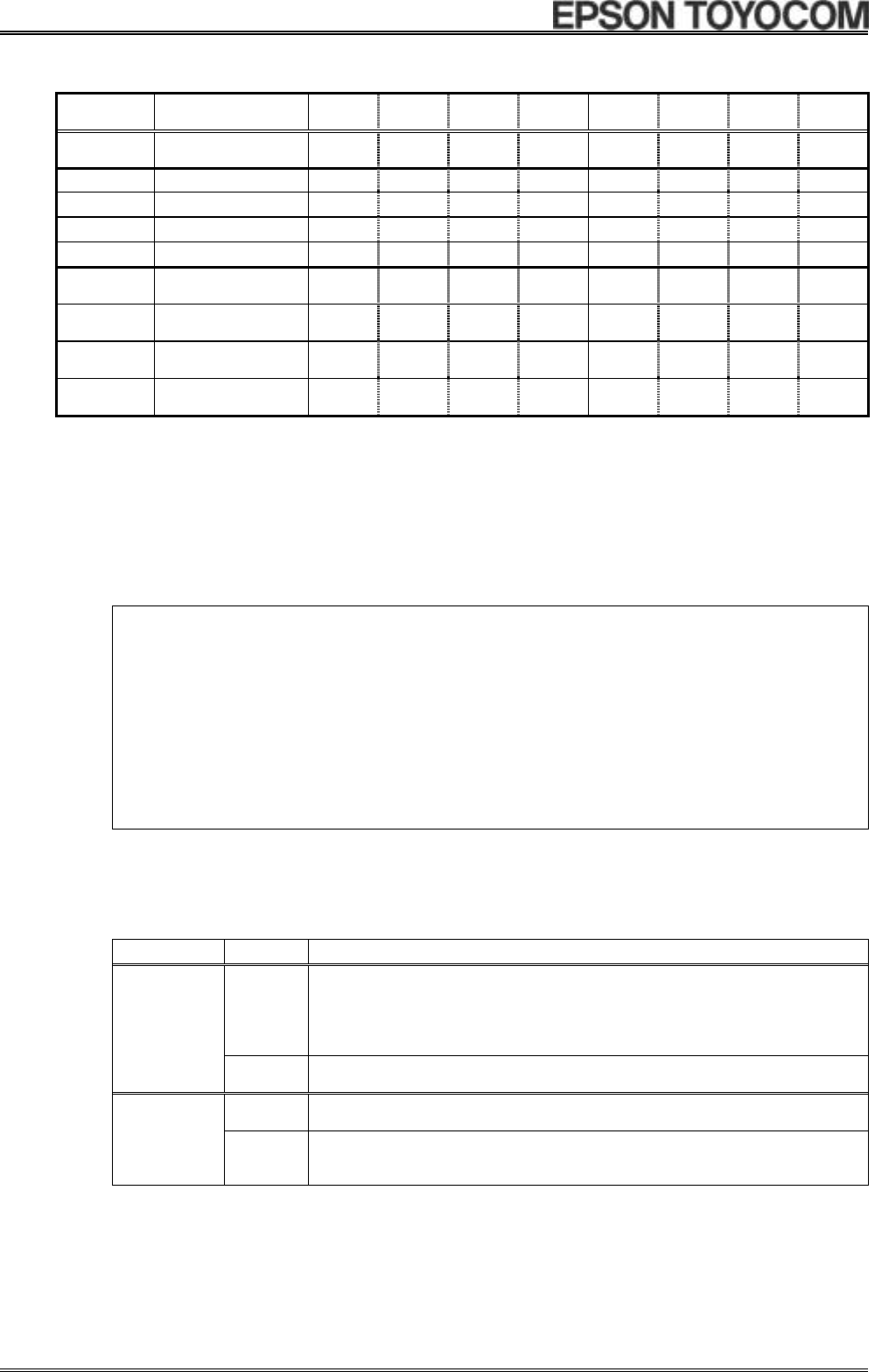

13.3.2. Alarm interrupt function registers

Address [h] Function bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

01 Control 2 0

×

0

TI / TP

AF

TF

AIE

TIE

03 Minutes

×

40 20 10 8 4 2 1

04 Hours

× ×

20 10 8 4 2 1

05 Days

× ×

20 10 8 4 2 1

06 Weekdays

× × × × ×

4 2 1

09 Minute Alarm

AE 40 20 10 8 4 2 1

0A Hour Alarm

AE

×

20 10 8 4 2 1

0B Day Alarm

AE

×

20 10 8 4 2 1

0C Weekday Alarm

AE

× × × ×

4 2 1

∗ Before entering settings for operations, we recommend writing a "0" to the AIE bit to prevent hardware interrupts

from occurring inadvertently while entering settings.

1) Alarm registers ( Reg − 09 [h] to 0C [h] )

The hour, minute, date or day when an alarm interrupt event will occur is set using this register and the AE

bit.

When the settings made in the alarm registers match the current time, the AF bit value is changed to "1". At

that time, if the AIE bit value has already been set to "1", the /INT pin goes low.

• AE bit

∗1) When the AE bit value is "1", the data concerning the setting in question is ignored and is not

subject to any comparison that would trigger an alarm interrupt.

To exclude a setting from possibly triggering an alarm interrupt, write "1" to the AE bit in the register

corresponding to the setting in question.

(Example) To leave [hour], [minute], and [day of week (weekday)] settings as possible alarm interrupt

triggers while excluding only the [day] setting from being a possible alarm interrupt trigger: → Write

80h (AE = "1") to the register used for the [day] setting register (the DAY Alarm

register, (Reg − 0B[h])).

∗2) If all four AE bits have a value of "1", no alarm interrupt events will occur.

2) AF bit ( Alarm Flag )

This is a flag bit that retains the result when an alarm interrupt event has been detected.

When this flag bit value is already set to "0", occurrence of an alarm interrupt event changes it to "1".

AF

Data Description

0

The AF bit is cleared to zero to prepare for the next status detection

∗ Clearing this bit to zero enables /AIRQ low output to be canceled (/AIRQ

remains Hi-Z) when an alarm interrupt event has occurred.

Write

1 This bit is invalid after a "1" has been written to it.

0 Alarm interrupt events are not detected.

Read

1

Alarm interrupt events are detected.

∗ Result is retained until this bit is cleared to zero.