RX − 8564 LC

Page − 22

ETM12E-01

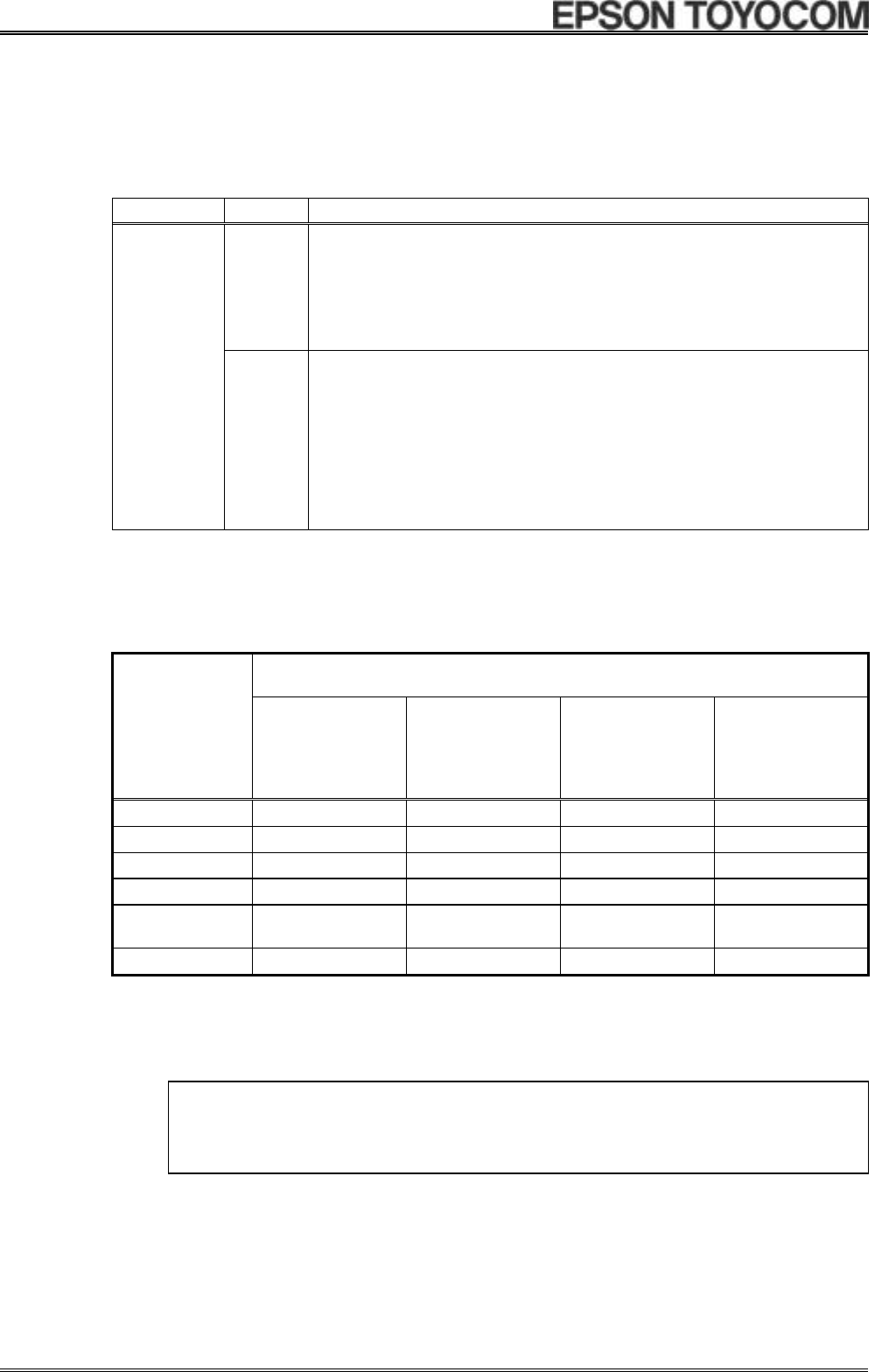

6) TIE bit ( Timer Interrupt Enable )

This bit is used to control output of interrupt signals from the /INT pin when a fixed-cycle timer interrupt

event has occurred.

When a "1" is written to this bit, occurrence of an interrupt event causes a low-level interrupt signal to be

output from /INT pin.

When a "0" is written to this bit, output from the /INT pin is prohibited (disabled).

TIE

Data Description

0

1) When a fixed-cycle timer interrupt event occurs, an interrupt signal is not

generated or is canceled (/INT status remains Hi-Z).

2) When a fixed-cycle timer interrupt event occurs, the interrupt signal is

canceled (/INT status changes from low to Hi-Z).

Write / Read

1

When a fixed-cycle timer interrupt event occurs, an interrupt signal is

generated (/INT status changes from Hi-Z to low).

∗ Level interrupt mode (single-shot operation)

If the TIE bit value is changed from "0" to "1" without first canceling the

interrupt event, the /INT pin immediately goes to low level.

13.2.3. Fixed-cycle timer interrupt interval (example)

The combination of the source clock settings (settings in TD1 and TD0) and fixed-cycle timer countdown

setting (Reg−C setting) sets the fixed-cycle timer interrupt interval, as shown in the following examples.

Source clock

Timer Counter

setting

4096 Hz

TD1,0 = 0,0

64 Hz

TD1,0 = 0,1

1 Hz

(When seconds

setting is updated)

TD1,0 = 1,0

1/60 Hz

(When minutes

setting is updated)

TD1,0 = 1,1

0

(00h) − − − −

1

(01h) 244.14 µs

15.625 ms 1 s 1 min

2

(02h) 488.28 µs

31.250 ms 2 s 2 min

3

(03h) 732.42 µs

46.875 ms 3 s 3 min

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

255

(FFh)

62.26 ms 3.984 s 255 s 255 min

• Fixed-cycle timer interrupt time error and fixed-cycle timer interrupt interval time

A fixed-cycle timer interrupt time error is an error in the selected source clock's

+0

/

−

1

interval time.

Accordingly, the fixed-cycle timer interrupt's interval (one cycle) falls within the following range in

relation to the set time.

Fixed-cycle timer interrupt's interval

(Fixed-cycle timer interrupt's set time(∗) − source clock interval) to (fixed-cycle timer interrupt set time)

∗) Fixed-cycle timer interrupt's set time = Source clock setting × Countdown timer setting for fixed-cycle timer

∗ The time actually set to the timer is adjusted by adding the time described above to the

communication time for the serial data transfer clock used for the setting.