HP Omnibook XT6050, XT/VT6200 Troubleshooting and Diagnostics 3-23

Power-On Self-Test

Note

If Quiet Boot is enabled in BIOS Setup (the default setting), press Esc during boot to see POST

messages.

When the notebook boots, its system BIOS runs a series of initialization routines and diagnostic tests

called POST (Power-On Self-Test). The BIOS will not boot the notebook’s operating system if certain

components fail the POST diagnostic tests. POST indicates progress by a sequence of codes; if an

error occurs, the BIOS displays a message and/or issues a beep code.

Note that not all POST messages indicate a failure in the notebook—some messages are for

information only. You should not necessarily interpret the failure of one or more POST tests as a

hardware, software, or firmware failure. If POST displays an error message or issues a beep code

indicating an error,

confirm the problem using other diagnostic tools.

First, confirm the failure by performing a “clean” boot, as described below: If the notebook fails to

restart with a clean boot, it requires repair.

1.

Remove all accessories, including SDRAM modules, floppy drive, port replicator, PC cards,

printer, external monitor, pointing device, and keyboard.

2.

Provide “clean” AC power—no auto adapter or unusual AC adapter configuration.

3.

Press the system-off switch to return the notebook to a known state.

4.

Press the blue sleep button to start the notebook.

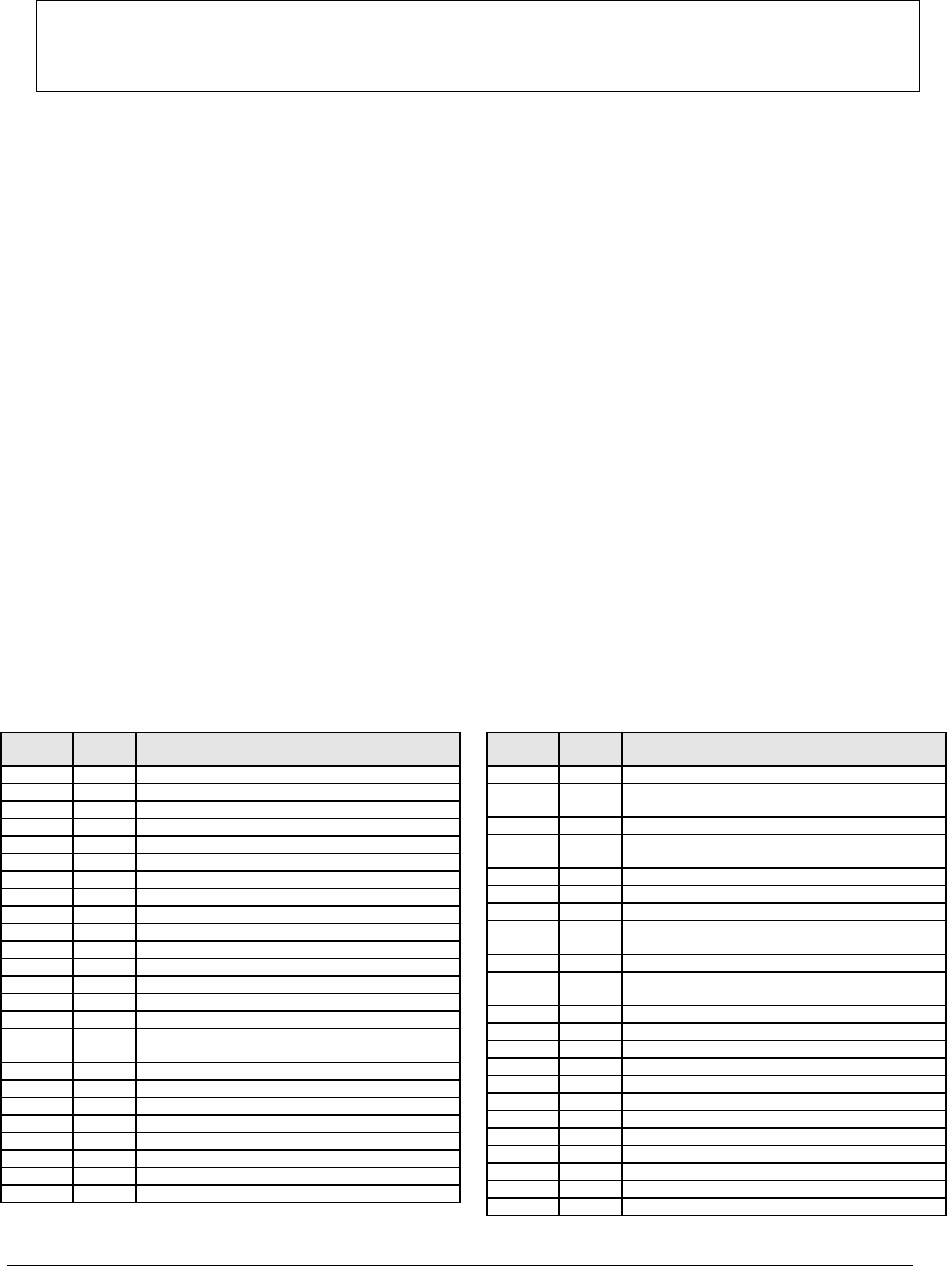

If the BIOS detects a terminal error condition, it halts POST after issuing a beep code and/or

displaying a message (see the following table). The beep code indicates the POST routine in which the

terminal error occurred.

Table 3-3. POST Terminal-Error Beep Codes

Bee

p

Codes*

Error

Code

POST Description

1 B4h One short beep before boot.

1-2 — Search for option ROMs.

1-1-1-3 02h Verify Real Mode.

1-1-1-4 03h Disable Non-Maskable Interrupt (NMI).

1-1-2-1 04h Get CPU type.

1-1-2-3 06h Initialize system hardware.

1-1-2-4 07h Disable shadow and execute code from ROM.

1-1-3-1 08h Initialize chipset with initial POST values.

1-1-3-2 09h Set IN POST flag.

1-1-3-3 0Ah Initialize CPU registers.

1-1-3-4 0Bh Enable CPU cache.

1-1-4-1 0Ch Initialize caches to initial POST values.

1-1-4-3 0Eh Initialize I/O component.

1-1-4-4 0Fh Initialize local bus IDE.

1-2-1-1 10h Initialize Power Management.

1-2-1-2 11h Load alternate registers with initial POST

values.

1-2-1-3 12h Restore CPU control word during warm boot.

1-2-1-4 13h Initialize PCI Bus Mastering devices.

1-2-2-1 14h Initialize keyboard controller.

1-2-2-3 16h BIOS ROM checksum.

1-2-2-4 17h Initialize cache before memory Auto size.

1-2-3-1 18h 8254 timer initialization.

1-2-3-3 1Ah 8237 DMA controller initialization.

1-2-4-1 1Ch Reset Programmable Interrupt Controller.

Bee

p

Codes*

Error

Code

POST Description

1-3-1-1 20h Test DRAM refresh.

1-3-1-3 22h Test 8742 Keyboard Controller (on

motherboard).

1-3-2-1 24h Set ES segment register to 4 GB.

1-3-3-1 28h Auto size DRAM; or wrong type or no RAM

installed.

1-3-3-2 29h Initialize POST Memory Manager.

1-3-3-3 2Ah Clear 512 kB base RAM.

1-3-4-1 2Ch RAM failure on address line xxxx.

1-3-4-3 2Eh RAM failure on data bits xxxx of low byte of

memory bus.

1-3-4-4 2Fh Enable cache before system BIOS shadow.

1-4-1-1 — RAM failure on data bits xxxx of high byte of

memory bus.

1-4-1-3 32h Test CPU bus-clock frequency.

1-4-1-4 33h Initialize Phoenix Dispatch Manager.

1-4-2-3 36h Warm start shut down.

1-4-3-1 38h Shadow system BIOS ROM.

1-4-3-3 3Ah Auto size cache.

1-4-4-1 3Ch Advanced configuration of chipset registers.

1-4-4-2 3Dh Load alternate registers with CMOS values.

2-1-1-2 41h Initialize extended memory for RomPilot.

2-1-1-3 42h Initialize interrupt vectors.

2-1-2-2 45h POST device initialization.

2-1-2-3 46h Check ROM copyright notice.

2-1-2-4 47h Initialize I20 support.