EM78P809N

8-Bit Microcontroller

Product Specification (V1.0) 07.26.2005

• 21

(This specification is subject to change without further notice)

Bit 0 ( WBE ) : Write buffer empty flag. Read only.

WBE = “0” : Write buffer empty

WBE = “1” : Not empty, set to “1” automatically when writing data to the data

buffer.

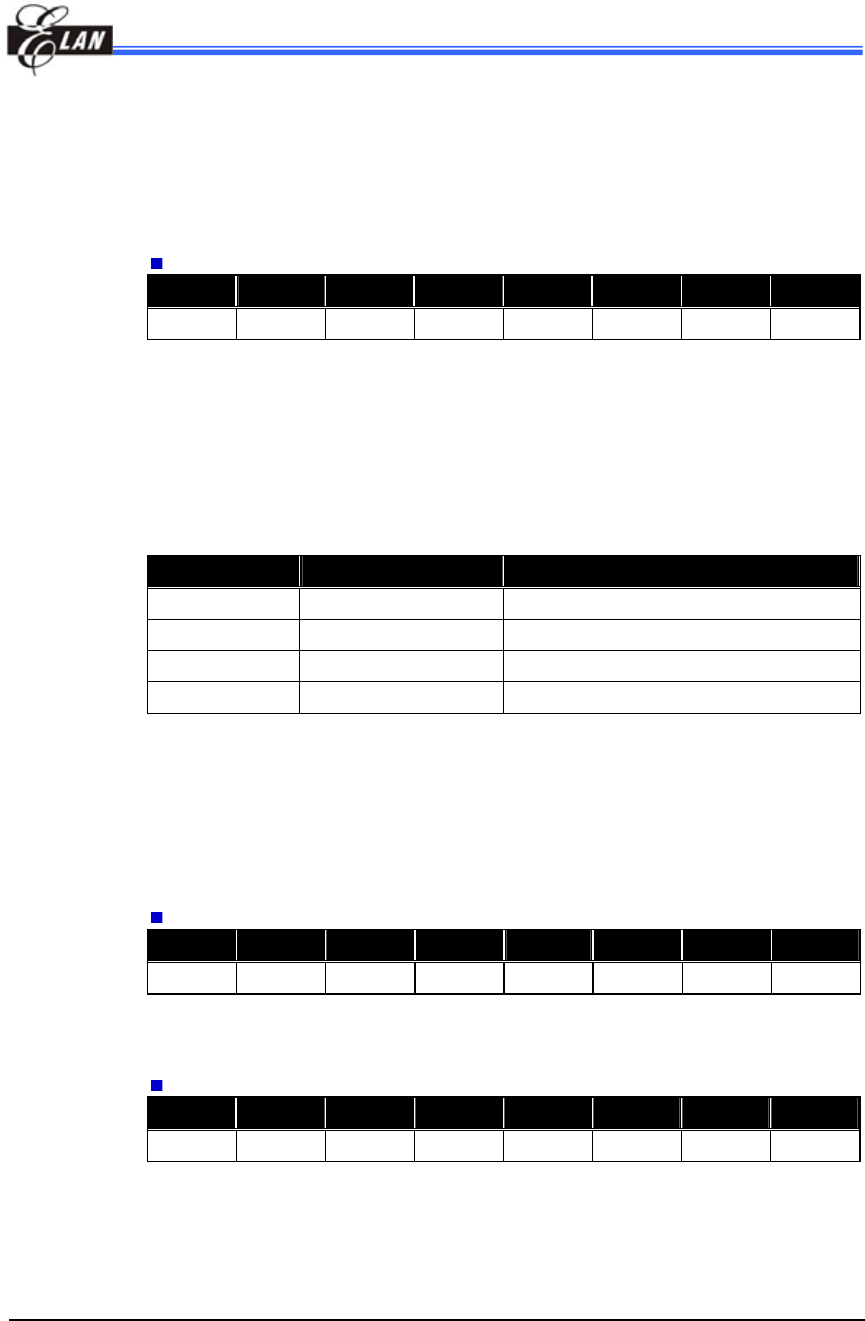

SPIC2 − SPI Control Register 2 (Address : 06h )

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SPIS 0 0 0 0 SPIM1 SPIM0 RBF

Bit 7 ( SPIS ) : SPI start shift, set the bit to “1” and shift register starts to shift. It is

cleared by hardware when shifting is finished. In transferring the

next data, it must be set to “1” again.

SPIS = “0” : Shift finish

SPIS = “1” : Shift starts

Bit 2 ~ Bit 1 ( SPIM1 ~ SPIM0) : SPI Transfer Mode Select

TC2CK1 TC2CK0 Transfer Mode

0 0 8-bit Transmit/Receive mode

0 1 8-bit Transmit mode

1 0 8-bit Receive mode

1 1 Reserved

Bit 0 ( RBF ) : Set to 1 by Buffer Full Detector, and cleared to 0 automatically when

reading data from the SPID register. RBF bit will be cleared by

hardware when enabling SPI. And RBF bit is read-only. Therefore,

reading the SPRL register is necessary to avoid data collision to

occur (DCOL).

SPID (SPI Data Buffer ( Address: 07h )

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

SPID7 SPID6 SPID5 SPID4 SPID3 SPID2 SPID1 SPID0

Bit 7 ~ Bit 0 ( SPID7 ~ SPID0 ) : SPI data buffer.

PHC1 − Pull High Control Register 1 ( Address: 0Ah )

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

- - /PHE81 /PHE80 /PHE63 /PHE62 /PHE61 /PHE60

Bit 5 ~ 4 ( /PHE81 ~ /PHE80 ) : bits 1, 0 of Port 8 Pull high enable bit

/PHE8x = “0” : Enable P8x pull high

/PHE8x = “1” : Disable P8x pull high