EM78P809N

8-Bit Microcontroller

54 •

Product Specification (V1.0) 07.26.2005

(This specification is subject to change without further notice)

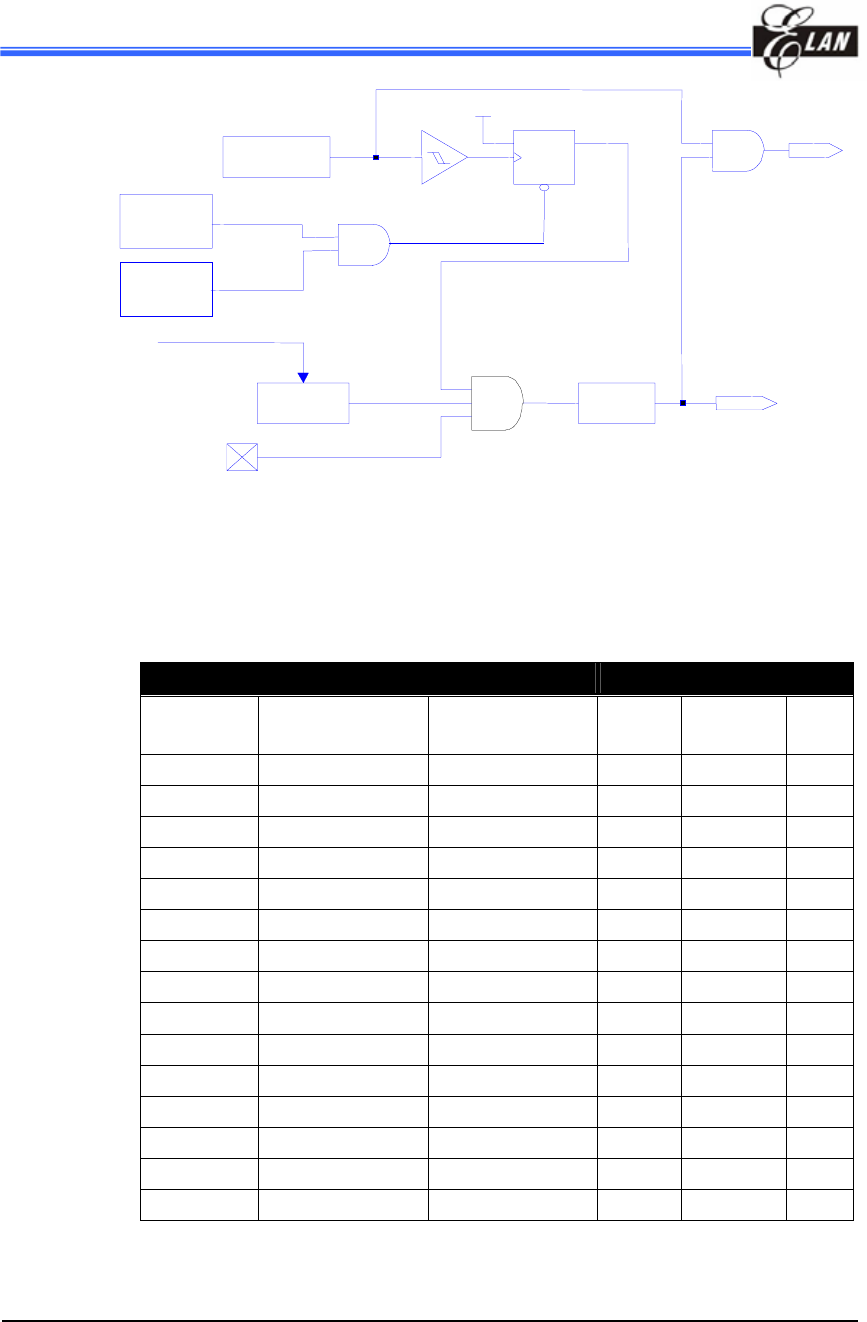

Voltage

Detector

Power-on

Reset

WDTE

Setup Time

VDD

DQ

CLK

CLR

CLK

RESET

WDT Timeout

WDT

/RESET

Oscillator

Fig. 29.Controller Reset Block Diagram

4.15 Interrupt

The EM78P809N has 15 interrupts (9 external, 6 internal) listed below:

Table 9.. Interrupt Vector

Interrupt Source Enable Condition Int. Flag Int. Vector Priority

Internal /

External

Reset - - 0000 High 0

Internal WDT WDTEN WDTIF 0003 1

External INT0 ENI + INT0EN=1 EXIEF0 0006 2

Internal TCC ENI + TCIE0=1 TCIF0 0009 3

External INT1 ENI + EXIE1=1 EXIF1 000F 4

Internal TBT ENI + TBIE=1 TBIF 0012 5

External UART Transmit ENI + UTIE=1 TBEF 0015 6

External UART Receive ENI + URIE=1 TBFF 0018 7

External UART Receive error ENI+UERRIE=1 UERRIF 001B 8

Internal TC3 ENI + TCIE3=1 TCIF3 0021 9

External SPI ENI + SPIE=1 SPIF 0024 10

Internal TC4 ENI + TCIE4=1 TCIF4 0027 11

External INT3 ENI + EXIE3=1 EXIF3 002A 12

External AD ENI + ADIE=1 ADIF 0030 13

Internal TC2 ENI + TCIE2=1 TCIF2 0033 14

External INT5 ENI + EXIE5=1 EXIF5 0036 Low 15

ISFR0, ISFR1 and ISFR2 are the interrupt status registers that record the interrupt

requests in the relative flags/bits. IMR1 and IMR2 are the interrupt mask registers. The

global interrupt is enabled by the ENI instruction and is disabled by the DISI instruction.