©2002 Inova Computers GmbH Page 2-9Doc. PD00581013.004

ICP-PIII

Configuration

CompactPCI

®

2

2.6 Timer / Counter

The IBM-compatible architecture configures the programmable timer / counter (Intel 8254-com-

patible) devices for system-specific functions as shown in Table 2.50.

The BIOS programs Timer 0 to generate an interrupt approximately every 55ms (18.2 times per

second.) This interrupt, known as the system timer tick, updates the BIOS clock and turns off the

floppy disk motor drive after a few seconds of inactivity for example.

The BIOS featured in Inova’s CPUs programs the system timer tick for PC compatibility. The inter-

rupt generated by the timer creates an interrupt request on IRQ0 of the programmable interrupt

controller (PIC) which is serviced by the CPU as interrupt vector 08h.

In addition, Timer 1 and Timer 2 are also initialised by the BIOS as necessary for the specific

‘processor board functions.

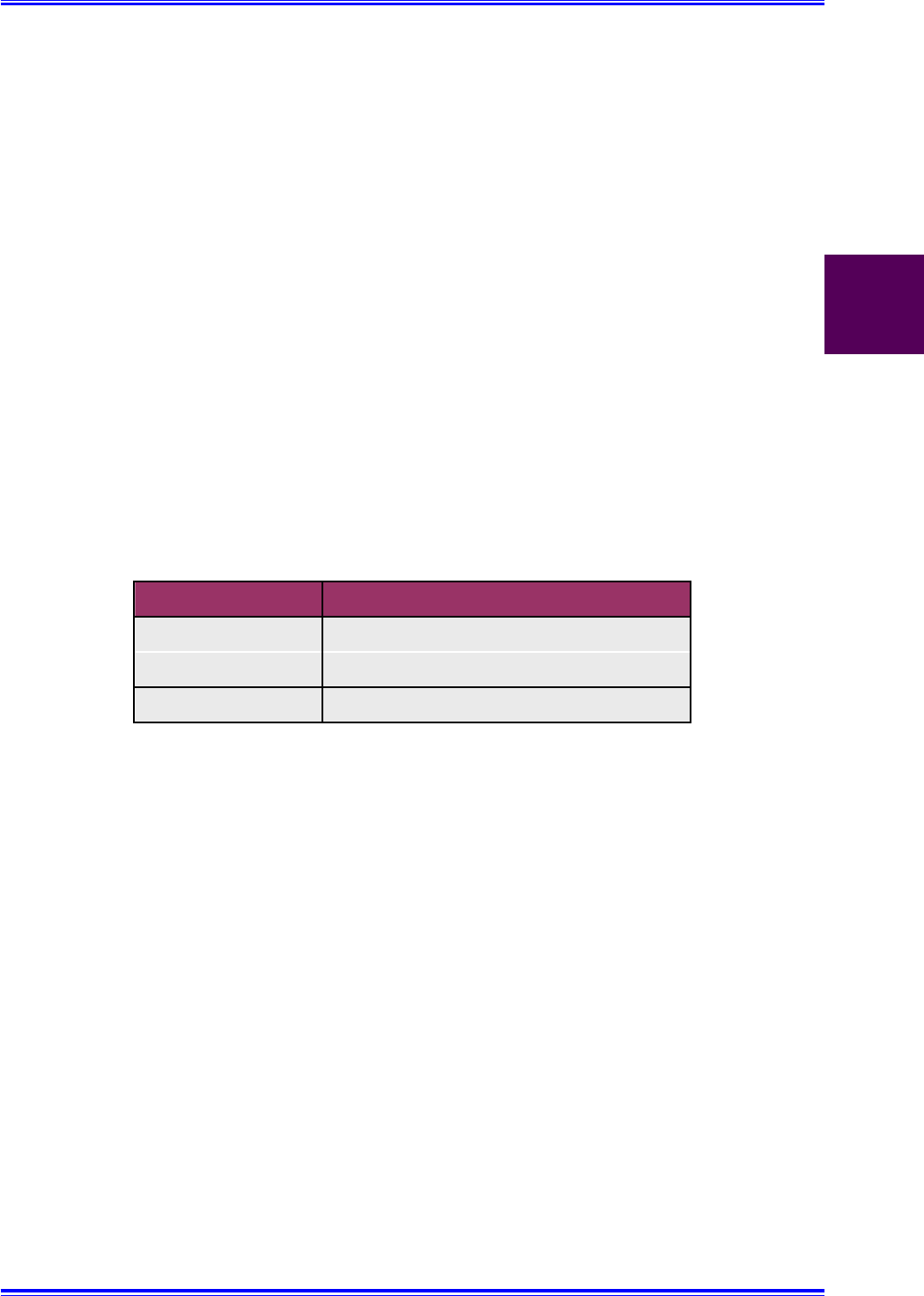

Table 2.50 Timer and Counter Functions

Timer Function/Assignment

Timer 0 System Timer, Periodic Interrupt (55 ms)

Timer 1 SDRAM Refresh

Timer 2 Speaker Frequency Generator

2.7 Watchdog

A three tier watchdog function with configurable timer is implemented in the ICP-PIII. Once the

timer has been set (between 64ms and 64x5min) the interrupt mode may be set. Either a Reset,

INIT, NMI or SMI interrupt is issued upon timeout.