©2002 Inova Computers GmbHPage 3-8 Doc. PD00581013.004

Interfaces

ICP-PIII

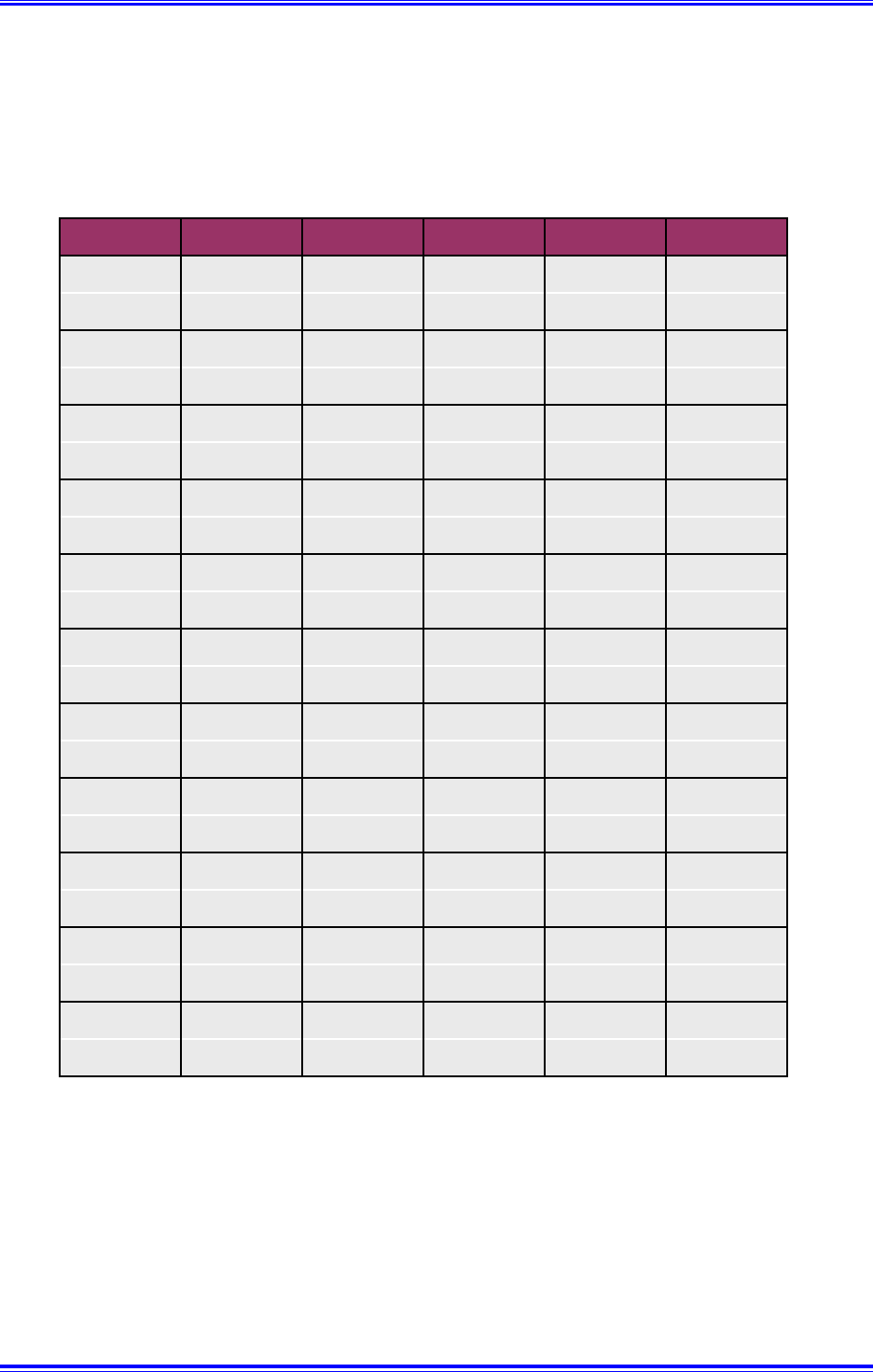

Table 3.06 Inova’s ICP-PIII 32-Bit CompactPCI J2 Pin Assignment for Rear I/O (C)

1)

: 5V TTL signals from serial I/O controller

2)

: Termination of USB lines on CPU. The +5V and GND signals need fuses and inductors for

decoupling (USB specification).

3)

: The 5V LPT signals need decoupling and pull-up resistors near the backplane LPT␣ 1

connector.

4)

: 5V open collector signal (5V/100mA)

5)

: Option “External Battery” (Note: battery must be removed from CPU board)

U

bat

= +3.4V to +3.6V

6)

: RS485 signals

Pin Nr Row A Row B Row C Row D Row E

J2-22 -----

J2-21 CLK6 GND FW_TPA+ FW_TPA- HCS0#

J2-20 CLK5 GND HADR0 GND HRST#

J2-19 GND GND HADR1 FW_TPB+ FW_TPB-

J2-18 LPT-STP

3)

LPT-PE

3)

HADR2 GND HCS1#

J2-17 LPT-AFD

3)

GND PRST# REQ6# GNT6#

J2-16 LPT-D0

3)

LPT-ACK

3)

[DEG# = LPT-

D0

]

GND (UBAT)

5)

J2-15 LPT-ERR

3)

GND

[FAL# = LPT-

D1

]

REQ5# GNT5#

J2-14 LPT-D1

3)

LPT-SLCT

3)

H5V(1A) GND HD0

J2-13 LPT-INIT

3)

GND V(I/O) HD1 HD2

J2-12 LPT-D2

3)

HIOW#

USB2-DATA+

2)

GND HD3

J2-11 LPT-SLIN

3)

GND V(I/O) HD4 HD5

J2-10 LPT-D3

3)

HIOR#

USB2-DATA-

2)

GND HD6

J2-09 LPT-D4

3)

GND V(I/O) HD7 HD8

J2-08 LPT-D5

3)

HIRQ15 HDMARQ GND HD9

J2-07

LPT-BUSY

3)

GND V(I/O) HD10 HD11

J2-06 LPT-D6

3)

- HDMACK GND HD12

J2-05 LPT-D7

3)

GND V(I/O) HD13 HD14

J2-04 V(I/O)

SPEAKER

4)

HIORDY# GND HD15

J2-03 CLK4 GND GNT3# REQ4# GNT4#

J2-02 CLK2 CLK3 SYSEN# GNT2# GNT3#

J2-01 CLK1 GND REQ1# GNT1# REQ2#