Interfaces

40 Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families

Datasheet Volume One of Two

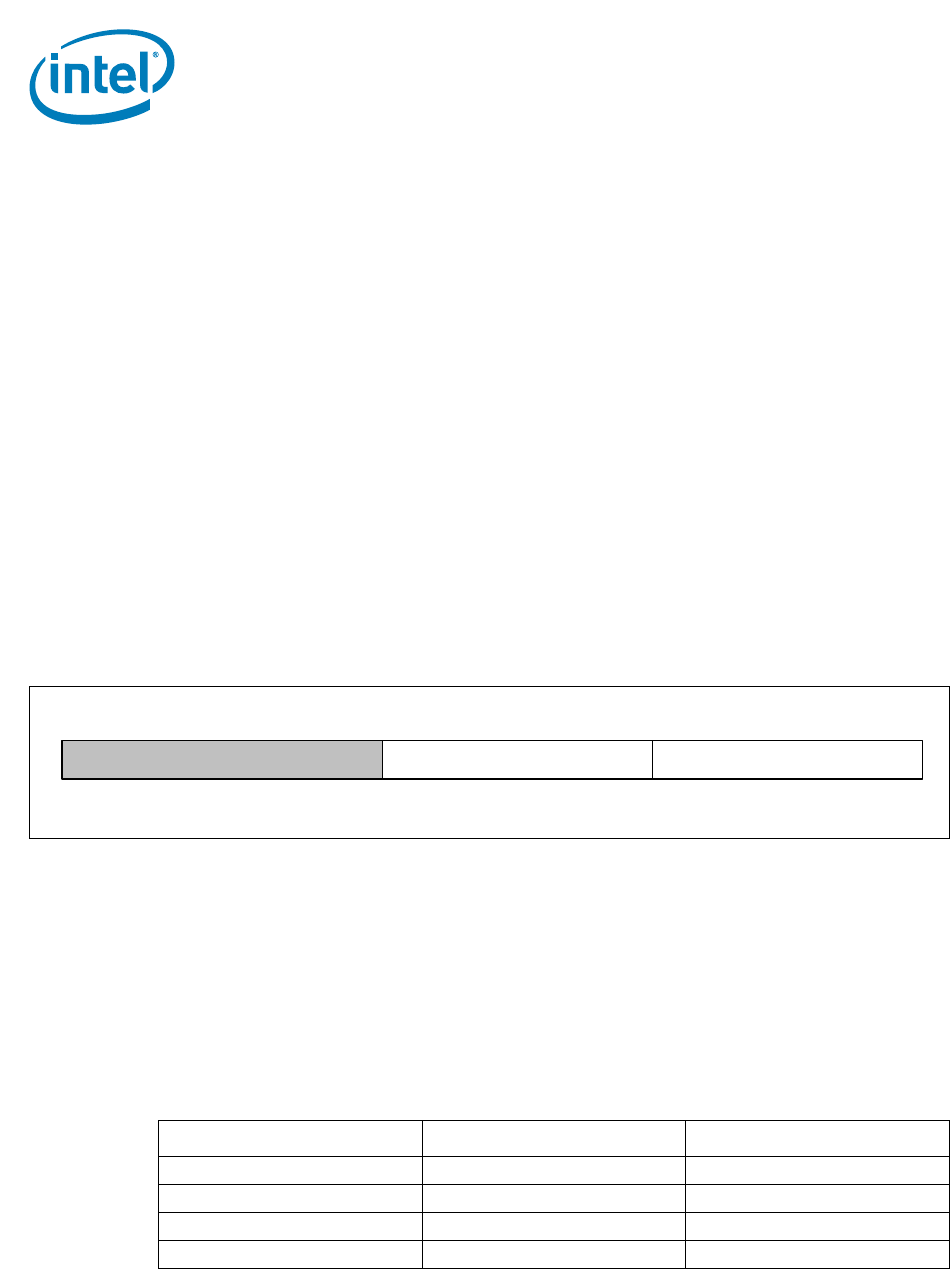

2.5.2.6.2 DRAM Thermal Estimation Configuration Data Read/Write

This feature is relevant only when activity-based DRAM temperature estimation

methods are being utilized and would apply to all the DIMMs on all the memory

channels. The write allows the PECI host to configure the ‘β’ and ‘θ’ variables in

Figure 2-12 for DRAM channel temperature filtering as per the equation below:

T

N

= β ∗ T

N

-1 + θ ∗ ΔEnergy

T

N

and T

N-1

are the current and previous DRAM temperature estimates respectively in

degrees Celsius, ‘β’ is the DRAM temperature decay factor, ‘ΔEnergy’ is the energy

difference between the current and previous memory transactions as determined by

the processor power control unit and ‘θ’ is the DRAM energy-to-temperature translation

coefficient. The default value of ‘β’ is 0x3FF. ‘θ’ is defined by the equation:

θ = (1 - β) ∗ (Thermal Resistance) ∗ (Scaling Factor)

The ‘Thermal Resistance’ serves as a multiplier for translation of DRAM energy changes

to corresponding temperature changes and may be derived from actual platform

characterization data. The ‘Scaling Factor’ is used to convert memory transaction

information to energy units in Joules and can be derived from system/memory

configuration information. Refer to the Intel® 64 and IA-32 Architectures Software

Developer’s Manual for methods to program and access ‘Scaling Factor’ information.

2.5.2.6.3 DRAM Rank Temperature Write

This feature allows the PECI host to program into the processor, the temperature for all

the ranks within a DIMM up to a maximum of four ranks as shown in Figure 2-13. The

DIMM index and Channel index are specified through the parameter field as shown in

Table 2-7. This write is relevant in platforms that do not have on-die or on-board DIMM

thermal sensors to provide memory temperature information or if the processor does

not have direct access to the DIMM thermal sensors. This temperature information is

used by the processor in conjunction with the activity-based DRAM temperature

estimations.

Figure 2-12. DRAM Thermal Estimation Configuration Data

Memory Thermal Estimation Configuration Data

RESERVED

1031

BETA VARIABLE

9 0

THETA VARIABLE

1920

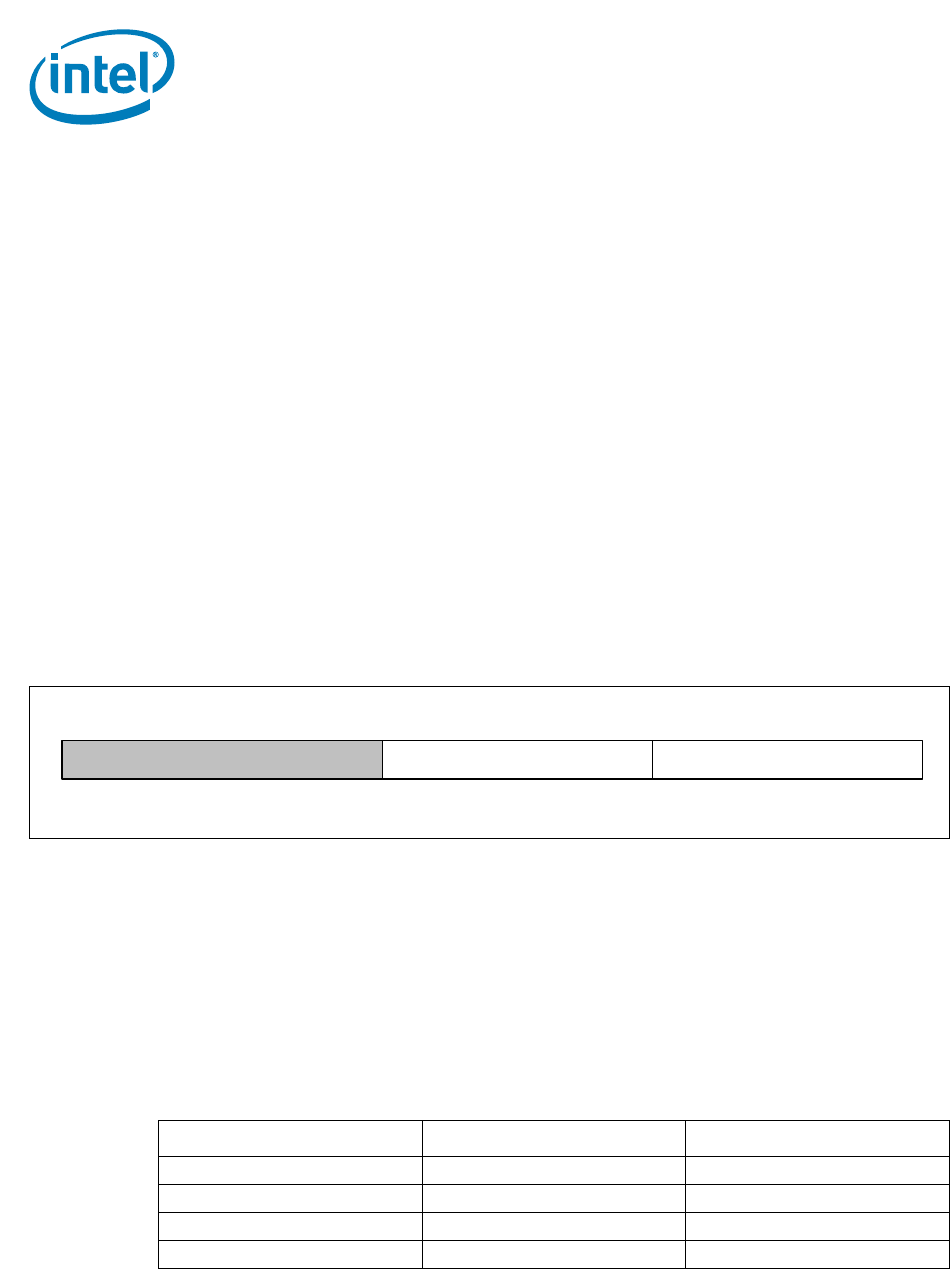

Table 2-7. Channel & DIMM Index Decoding

Index Encoding Physical Channel# Physical DIMM#

000 0 0

001 1 1

010 2 2

011 3 Reserved