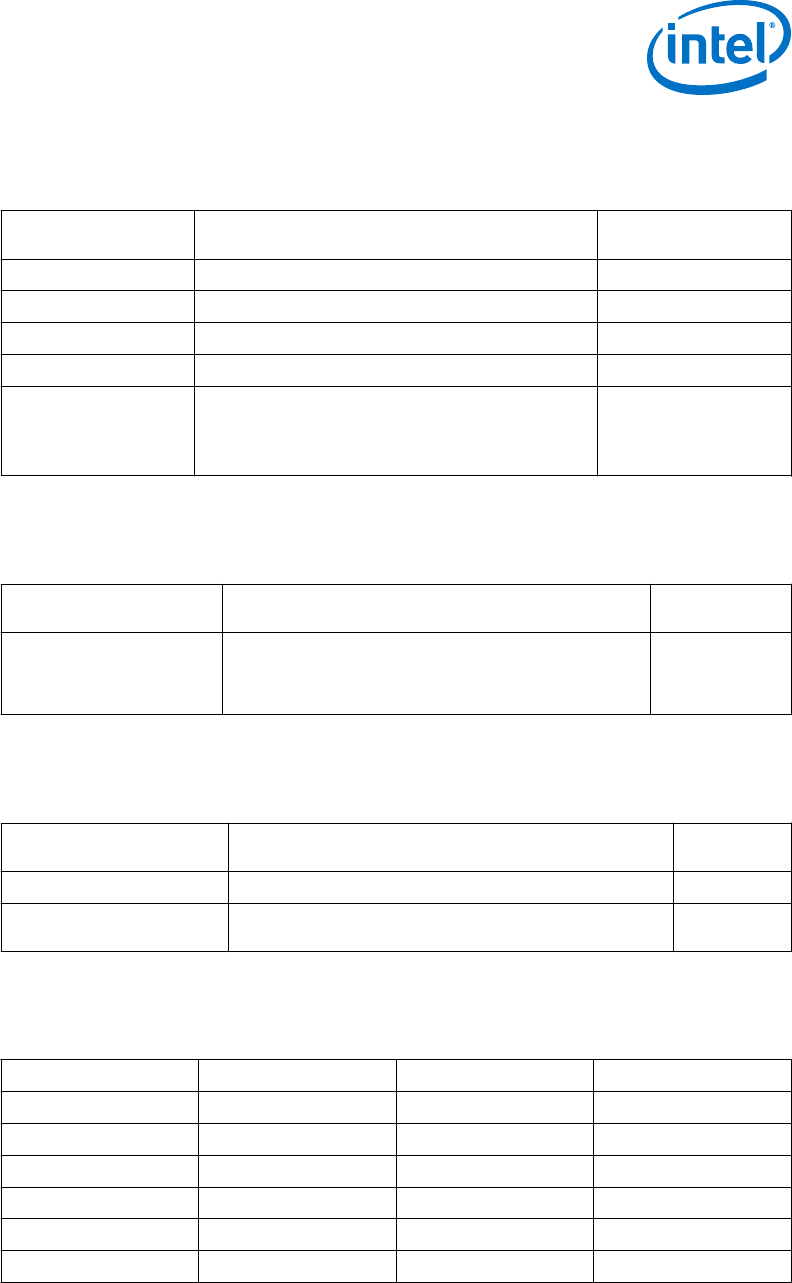

Processor Power Signals

Table 41. Processor Power Signals

Signal Name Description Direction / Buffer

Type

VCC Processor core power rail. Ref

VCCIO_OUT Processor power reference for I/O. Ref

VDDQ Processor I/O supply voltage for DDR3. Ref

VCOMP_OUT Processor power reference for PEG/Display RCOMP. Ref

VIDSOUT

VIDSCLK

VIDALERT#

VIDALERT#, VIDSCLK, and VIDSCLK comprise a three

signal serial synchronous interface used to transfer

power management information between the

processor and the voltage regulator controllers.

Input GTL/ Output Open

Drain

Output Open Drain

Input CMOS

Sense Signals

Table 42. Sense Signals

Signal Name Description Direction /

Buffer Type

VCC_SENSE

VSS_SENSE

VCC_SENSE and VSS_SENSE provide an isolated, low-

impedance connection to the processor input V

CC

voltage

and ground. The signals can be used to sense or measure

voltage near the silicon.

O

A

Ground and Non-Critical to Function (NCTF) Signals

Table 43. Ground and Non-Critical to Function (NCTF) Signals

Signal Name Description Direction /

Buffer Type

VSS Processor ground node GND

VSS_NCTF

Non-Critical to Function: These pins are for package

mechanical reliability.

—

Processor Internal Pull-Up / Pull-Down Terminations

Table 44. Processor Internal Pull-Up / Pull-Down Terminations

Signal Name Pull Up / Pull Down Rail Value

BPM[7:0] Pull Up VCCIO_TERM 40–60 Ω

PREQ# Pull Up VCCIO_TERM 40–60 Ω

TDI Pull Up VCCIO_TERM 30–70 Ω

TMS Pull Up VCCIO_TERM 30–70 Ω

CFG[17:0] Pull Up VCCIO_OUT 5–8 kΩ

CATERR# Pull Up VCCIO_TERM 30–70 Ω

6.11

6.12

6.13

6.14

Signal Description—Processor

Desktop 4th Generation Intel

®

Core

™

Processor Family, Desktop Intel

®

Pentium

®

Processor Family, and Desktop Intel

®

Celeron

®

Processor Family

December 2013 Datasheet – Volume 1 of 2

Order No.: 328897-004 89