34

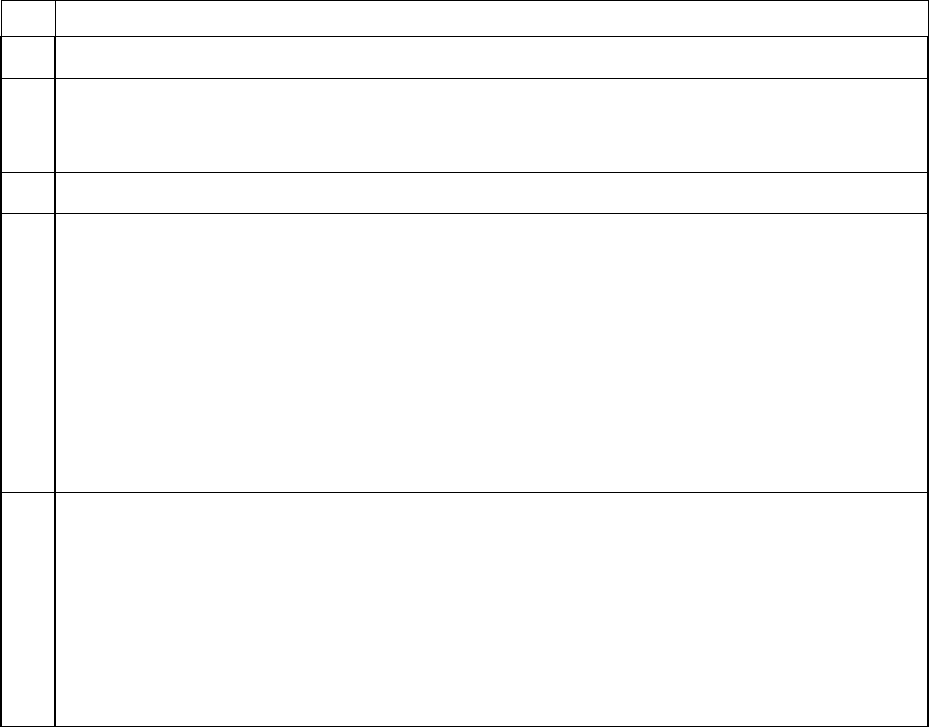

7.2.2 WDT Configuration Register (60h)

Offset: 60-61h

Default Value: 00h

Size: 16 bits

Attribute: R/W

Bit Description

15-6

Reserved

5

WDT_OUTPUT: Output Enable

This bit indicates whether or not the WDT will toggle the WDT_TOUT# pin if the WDT times

out.

4-3

Reserved

2

WDT_PRE_SEL: Prescaler Select

The WDT provides two options for prescaling the main down counter. The preload values

are loaded into the main down counter right justified. The prescaler adjusts the starting point

of the 35 bit down counter.

0 – The 20 bit preload value is loaded into bits 34:15 of the main down counter. The resulting

timer clock is PCI clock (33MHz) divided by 2

15

. The approximate clock generated

1KHz.(1ms to 10 min)

1 – The 20 bit preload value is loaded into bits 24:15 of the main down counter. The resulting

timer clock is PCI clock (33MHz) divided by 2

5

. The approximate clock generated 1MHz.(1µs

to 1sec)

1-0

WDT_INT_TYPE

The desired type of interrupt if the WDT reaches the end of the first stage without being

reloaded.

00 = IRQ (APIC 1, IRQ 10)

01 = Reserved

10 = SMI

11 = Disabled

7.2.3 WDT Lock Register (68h)

Offset: 68h

Default Value: 00h

Size: 8 bits

Attribute: R/W