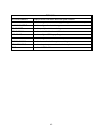

35

Bit Description

7:3

Reserved

2

WDT_TOUT_CNF: Timeout configuration

0 – Watchdog Timer Mode

1 – Free Running Mode

1

WDT_ENABLE: Watchdog Enable

0 – Disabled

1 - Enabled

0

WDT_LOCK

Setting this bit will lock values of this register until a hard reset occurs or power is cycled.

0 – Unlocked

1 - Locked

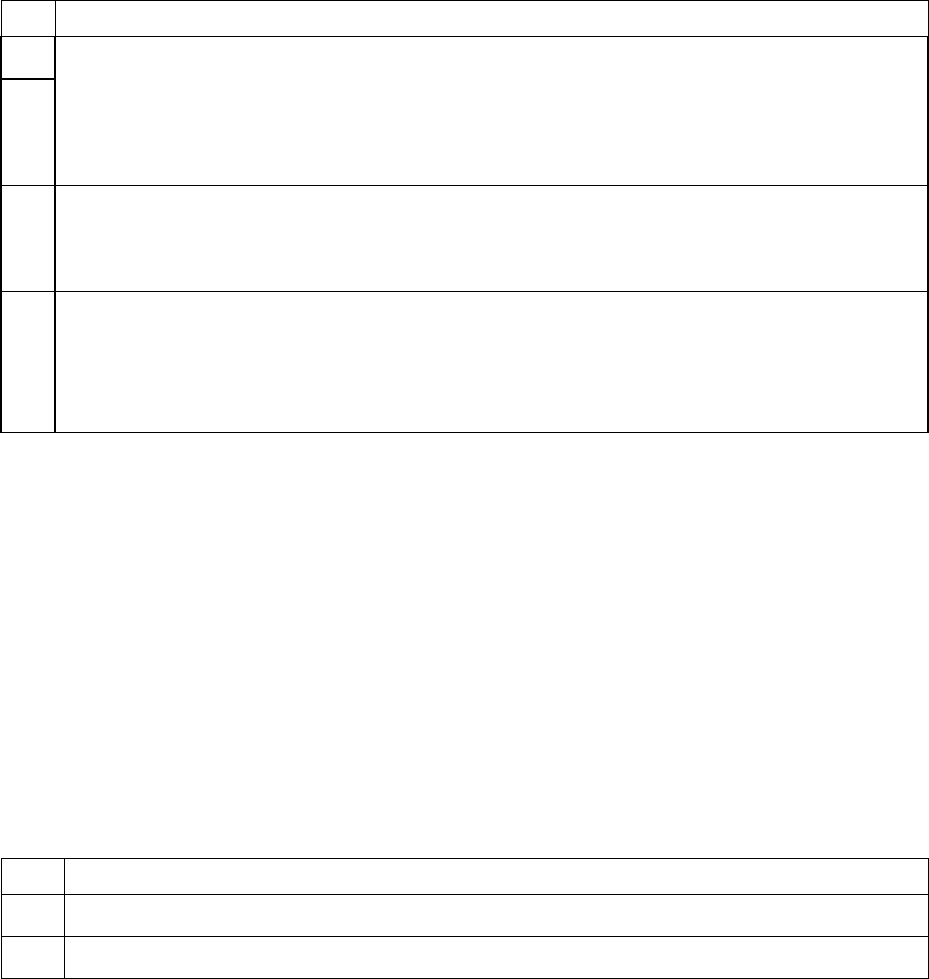

7.3 Memory Mapped Registers

The following registers control the preload values and reload status of the watchdog timer controller.

These register locations are offsets from the value of the base address register and appears at Bus:0

Dev:29 Func:4 Reg:10-13.

7.3.1 Preload Value 1 (BAR+00h)

Offset: BAR+00h

Default Value: FFFFFh

Size: 32 bits

Attribute: R/W

Bit Description

31:20

Reserved

19:0

Preload_Value_1

7.3.2 Preload Value 2 (BAR+04h)

Offset: BAR+04h

Default Value: FFFFFh

Size: 32 bits

Attribute: R/W