Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

December 1995COPYRIGHT

INTEL CORPORATION1996 Order Number290414-003

UPI-C42UPI-L42

UNIVERSAL PERIPHERAL INTERFACE

CHMOS 8-BIT SLAVE MICROCONTROLLER

Y

Pin Software and Architecturally

Compatible with all UPI-41 and UPI-42

Products

Y

Low Voltage Operation with the UPI-

L42

Full 33V Support

Y

Hardware A20 Gate Support

Y

Suspend Power Down Mode

Y

Security Bit Code Protection Support

Y

8-Bit CPU plus ROMOTP EPROM RAM

IO TimerCounter and Clock in a

Single Package

Y

4096 x 8 ROMOTP 256 x 8 RAM 8-Bit

TimerCounter 18 Programmable IO

Pins

Y

DMA Interrupt or Polled Operation

Supported

Y

One 8-Bit Status and Two Data

Registers for Asynchronous Slave-to-

Master Interface

Y

Fully Compatible with all Intel and Most

Other Microprocessor Families

Y

Interchangeable ROM and OTP EPROM

Versions

Y

Expandable IO

Y

Sync Mode Available

Y

Over 90 Instructions 70% Single Byte

Y

Quick Pulse Programming Algorithm

Fast OTP Programming

Y

Available in 40-Lead Plastic 44-Lead

Plastic Leaded Chip Carrier and

44-Lead Quad Flat Pack Packages

(See Packaging Spec Order

240800 Package Type P N

and S)

The UPI-C42 is an enhanced CHMOS version of the industry standard Intel UPI-42 family It is fabricated on

Intel’s CHMOS III-E process The UPI-C42 is pin software and architecturally compatible with the NMOS UPI

family The UPI-C42 has all of the same features of the NMOS family plus a larger user programmable memory

array (4K) hardware A20 gate support and lower power consumption inherent to a CHMOS product

The UPI-L42 offers the same functionality and socket compatibility as the UPI-C42 as well as providing low

voltage 33V operation

The UPI-C42 is essentially a ‘‘slave’’ microcontroller or a microcontroller with a slave interface included on the

chip Interface registers are included to enable the UPI device to function as a slave peripheral controller in the

MCS Modules and iAPX family as well as other 8- 16- and 32-bit systems

To allow full user flexibility the program memory is available in ROM and One-Time Programmable EPROM

(OTP)

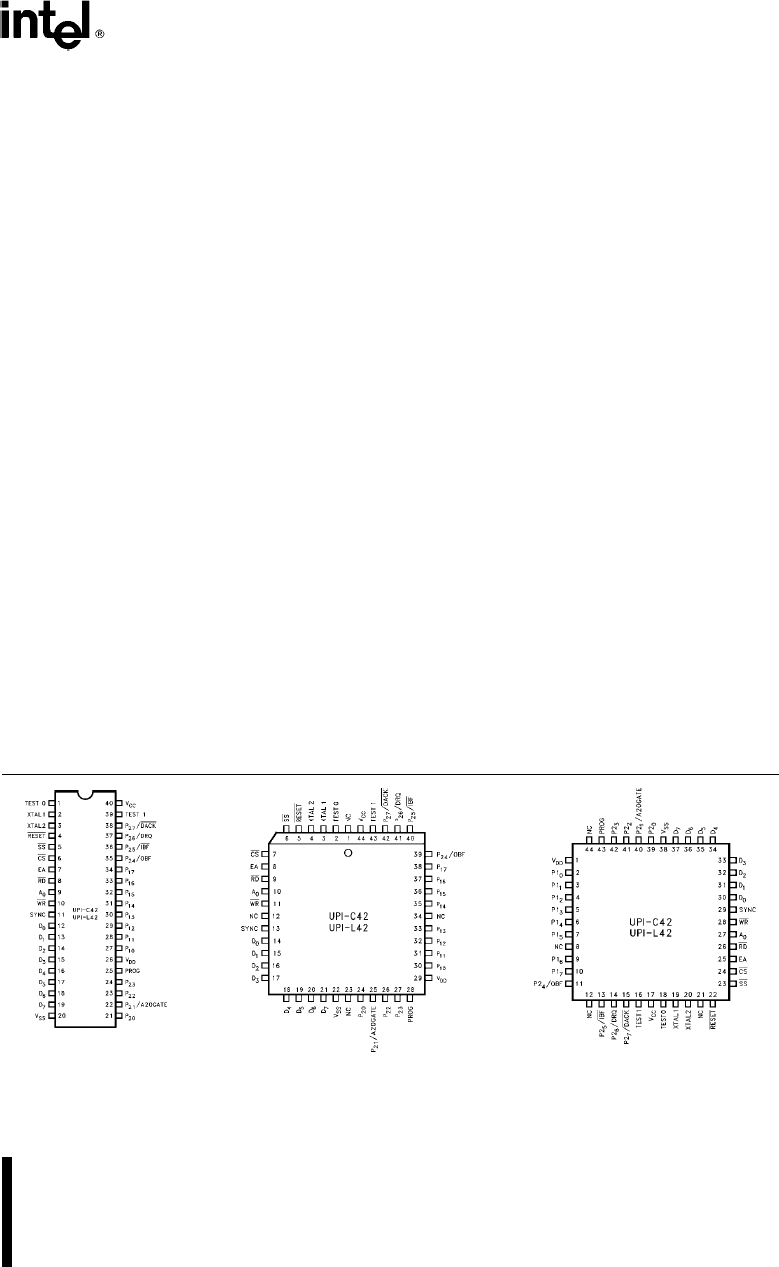

290414–1

Figure 1 DIP Pin

Configuration

290414–2

Figure 2 PLCC Pin Configuration

290414–3

Figure 3 QFP Pin Configuration