Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 22

IIR – Interrupt Identifier Register (Addr = 2)

The Interrupt Identifier Register (IIR) identifies the existence and type of up to five prioritized pending

interrupts. Four priority levels are set to assist interrupt processing in the host. The four levels, in

order of decreasing priority, are Highest: Receiver Line Status, 2: Receiver Data Available or

Receiver Character Timeout. 3: TX Buffer Empty, and 4: Modem Status.

When the IIR is accessed, the modem freezes all interrupts and indicates the highest priority interrupt

pending to the host. Any change occurring in interrupt conditions are not indicated until this access is

complete.

Bits 7-6 FIFO Mode

These two bits copy FCR0.

Bits 5-4 Not Used

Always 0.

Bits 3-1 Highest Priority Pending Interrupt

These three bits identify the highest priority pending interrupt (Table 4-2). Bit 3 is applicable

only when FIFO mode is selected; otherwise, bit 3 is a 0.

Bit 0 Interrupt Pending

When this bit is a 0, an interrupt is pending; IIR bits 1-3 can be used to determine the source

of the interrupt. When this bit is a 1, an interrupt is not pending.

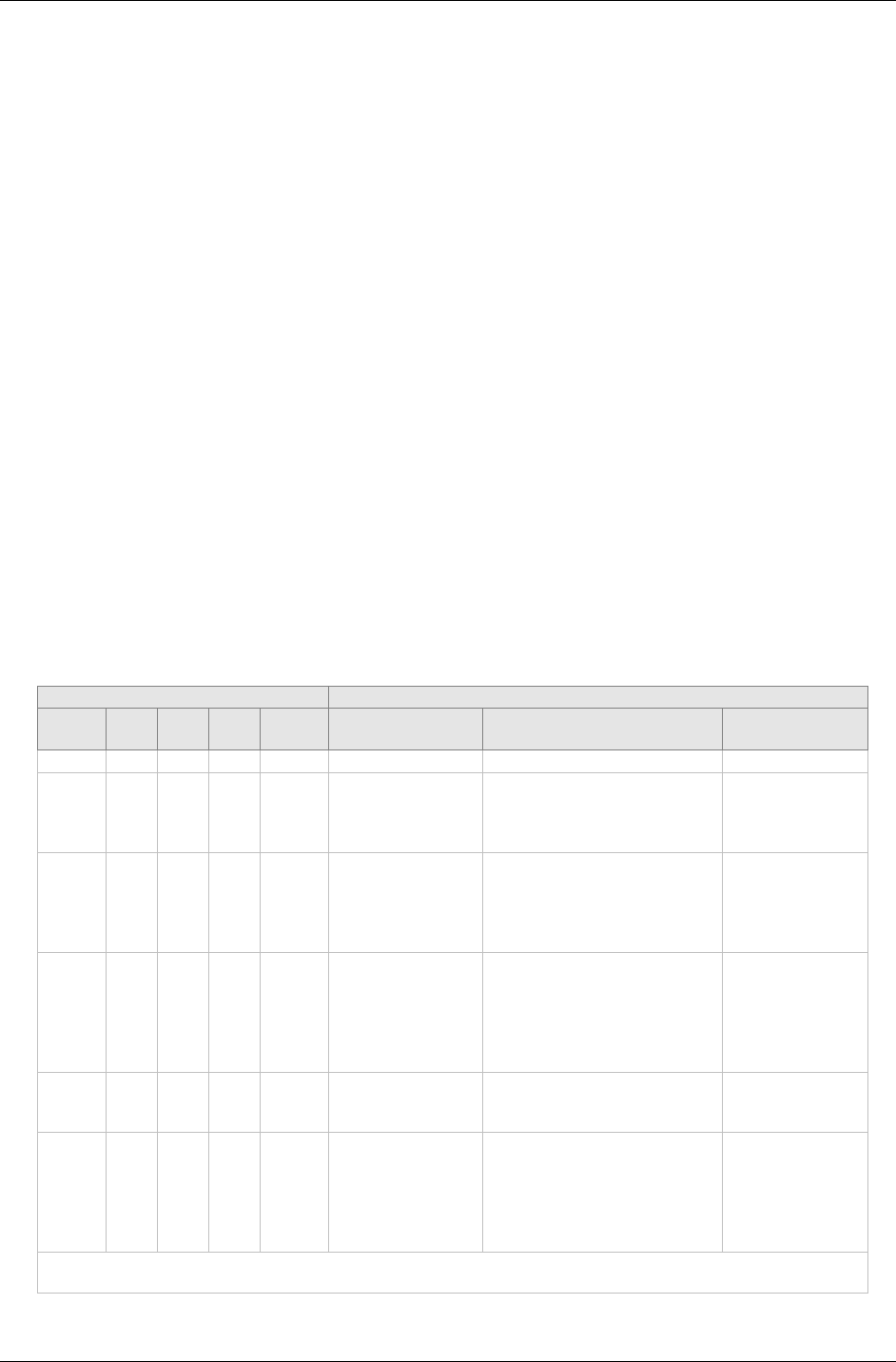

Table 4–2. Interrupt Sources and Reset Control

Interrupt Identification Register Interrupt Set and Reset Functions

Bit 3

(Note 1)

Bit 2 Bit 1 Bit 0 Priority

Level

Interrupt Type Interrupt Source Interrupt Reset

Control

0 0 0 1 — None None —

0 1 1 0 Highest Receiver Line

Status

Overrun Error (OE) (LSR1),

Parity Error (PE) (LSR2),

Framing Error (FE) (LSR3),

or Break Interrupt (BI) (LSR4)

Reading the LSR

0 1 0 0 2 Received Data

Available

Received Data Available

(LSR0)

or RX FIFO Trigger Level

(FCR6-FCR7)

Reached

1

Reading the RX

Buffer or the RX

FIFO drops

below the

Trigger Level

1 1 0 0 2 Character Timeout

Indication

1

The RX FIFO contains at

least 1 character and no

characters have been

removed from or input to the

RX FIFO during the last 4

character times.

Reading the RX

Buffer

0 0 1 0 3 TX Buffer Empty TX Buffer Empty Reading the IIR

or writing to the

TX Buffer

0 0 0 0 4 Modem Status Delta CTS (DCTS) (MSR0),

Delta DSR (DDST) (MSR1),

Trailing Edge Ring Indicator

(TERI) (MSR3), or Delta

DCD (DCD) (MSR4)

Reading the

MSR

Notes:

1. FIFO Mode only.