Chapter 10 Digital Routing and Clock Generation

© National Instruments Corporation 10-9 NI 6238/6239 User Manual

input on each rising edge of a filter clock. M Series devices use an onboard

oscillator to generate the filter clock with a 40 MHz frequency.

Note NI-DAQmx only supports filters on counter inputs.

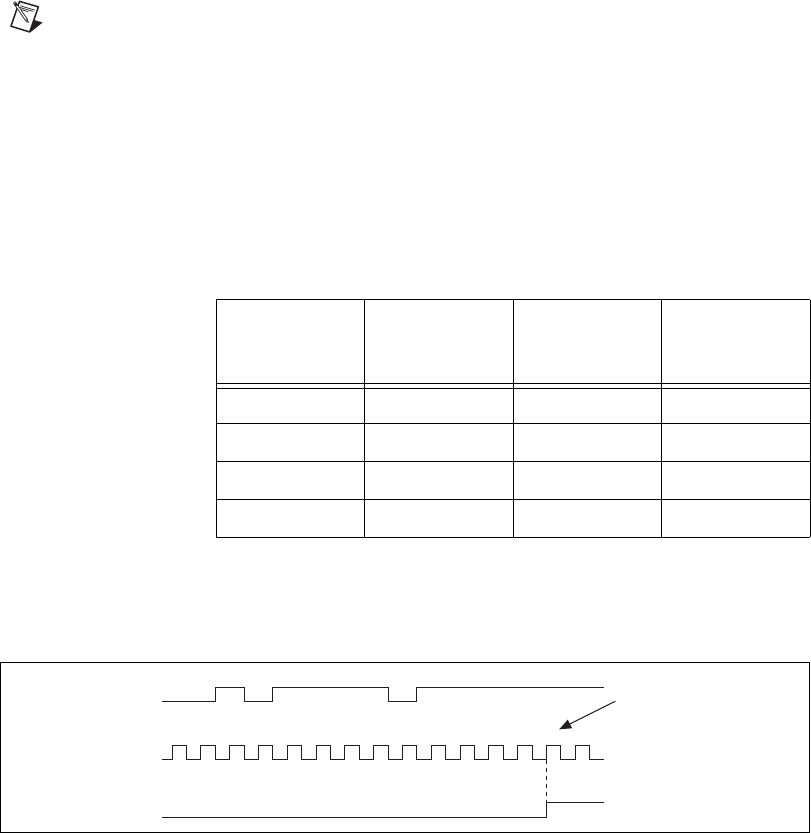

The following is an example of low-to-high transitions of the input signal.

High-to-low transitions work similarly.

Assume that an input terminal has been low for a long time. The input

terminal then changes from low-to-high, but glitches several times. When

the filter clock has sampled the signal high on N consecutive edges, the

low-to-high transition is propagated to the rest of the circuit. The value of

N depends on the filter setting; refer to Table 10-3.

The filter setting for each input can be configured independently. On power

up, the filters are disabled. Figure 10-4 shows an example of a low-to-high

transition on an input that has its filter set to 125 ns (N = 5).

Figure 10-4. Filter Example

Enabling filters introduces jitter on the input signal. For the 125 ns and

6.425 µs filter settings, the jitter is up to 25 ns. On the 2.55 ms setting, the

jitter is up to 10.025 µs.

Table 10-3. Filters

Filter Setting

N (Filter

Clocks Needed

to Pass Signal)

Pulse Width

Guaranteed to

Pass Filter

Pulse Width

Guaranteed to

Not Pass Filter

125 ns 5 125 ns 100 ns

6.425 µs 257 6.425 µs 6.400 µs

2.55 ms ~101,800 2.55 ms 2.54 ms

Disabled — — —

1231 4 12345

RTSI, PFI, or

PXI_STAR Terminal

Filter Clock

(40 MHz)

Filtered Input

Filtered input goes high

when terminal is sampled

high on five consecutive

filter clocks.