Chapter 4 Analog Input

NI 6238/6239 User Manual 4-20 ni.com

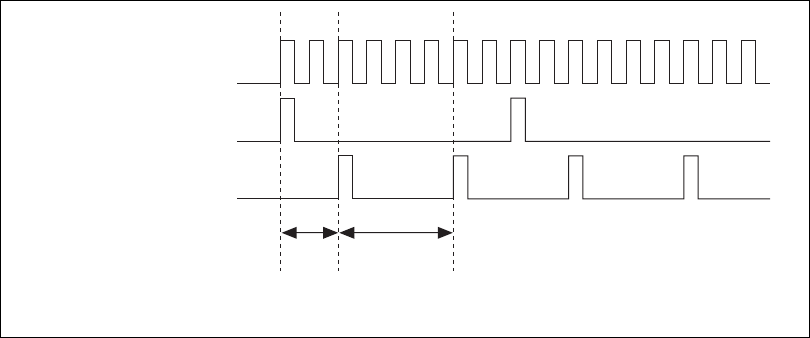

Figure 4-12. ai/SampleClock and ai/ConvertClock

Other Timing Requirements

The sample and conversion level timing of M Series devices work such that

clock signals are gated off unless the proper timing requirements are met.

For example, the device ignores both ai/SampleClock and ai/ConvertClock

until it receives a valid ai/StartTrigger signal. When the device recognizes

an ai/SampleClock pulse, it ignores subsequent ai/SampleClock pulses

until it receives the correct number of ai/ConvertClock pulses.

Similarly, the device ignores all ai/ConvertClock pulses until it recognizes

an ai/SampleClock pulse. After the device receives the correct number of

ai/ConvertClock pulses, it ignores subsequent ai/ConvertClock pulses until

it receives another ai/SampleClock. Figure 4-13 shows timing sequences

for a four-channel acquisition (using AI channels 0, 1, 2, and 3) and

demonstrates proper and improper sequencing of ai/SampleClock and

ai/ConvertClock.

It is also possible to use a single external signal to drive both

ai/SampleClock and ai/ConvertClock at the same time. In this mode, each

tick of the external clock will cause a conversion on the ADC. Figure 4-13

shows this timing relationship.

ai/ConvertClockTimebase

ai/SampleClock

ai/ConvertClock

Delay

From

Sample

Clock

Convert

Period