DDR3THIN-MN-XXX 52 Doc. Rev. 1.11

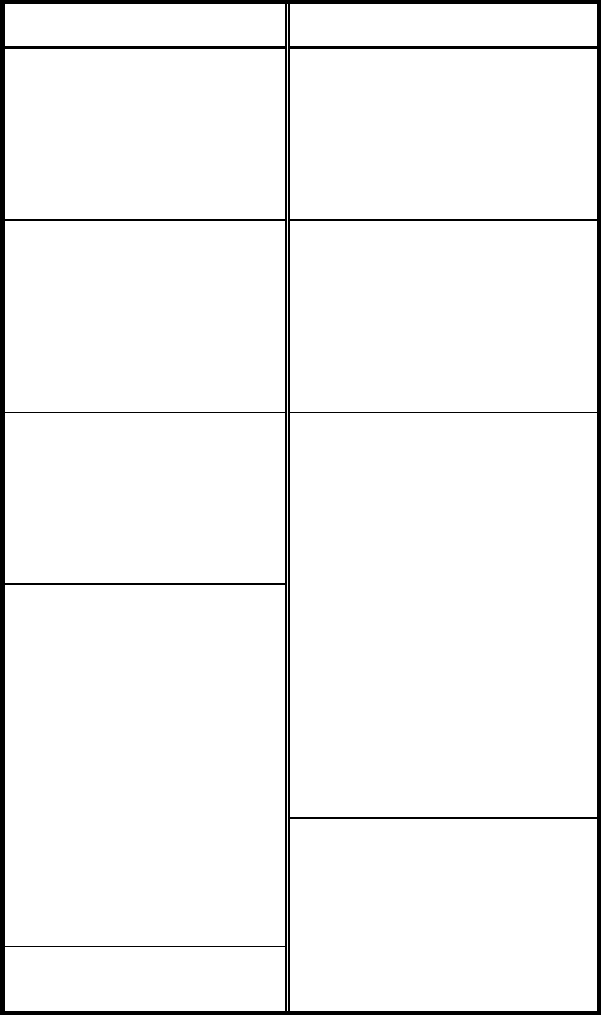

Group

Name

Signal

Name

TLA

Input

Group

Name

Signal

Name

TLA

Input

ChkBits

CB7 M_A1:5 ChkBits_1

1_CB7 S2_D3:5

CB6 M_A1:4 1_CB6 S2_D3:4

CB5 M_A1:0 1_CB5 S2_D3:0

CB4 M_A0:7 1_CB4 S2_D2:7

CB3 M_A1:6 1_CB3 S2_D3:6

CB2 M_A1:3 1_CB2 S2_D3:3

CB1 M_CK1 1_CB1 S2_Q0

CB0 M_A0:5 1_CB0 S2_D2:5

Strobes

2

DQS8 M_A1:2 Strobes_1

2

1_DQS8 S2_D3:2

DQS7 S_A2:6 1_DQS7 S2_A0:6

DQS6 S_A3:5 1_DQS6 S2_A1:5

DQS5 S_CK1 1_DQS5 S2_CK2

DQS4 M_C2:3 1_DQS4 S2_C2:3

DQS3 M_A0:0 1_DQS3 S2_D2:0

DQS2 S_C3:0 1_DQS2 S2_E3:0

DQS1 S_E3:6 1_DQS1 S2_E1:6

DQS0 S_E2:4 1_DQS0 S2:E0:4

DataMasks DM7 S_A2:4 Address

2

BA2 M_A3:0

DM6 S_A3:6 BA1 M_C3:7

DM5 S_A1:0 BA0 M_C1:6

DM4 M_C2:0 A15 M_CK0

DM3 M_A0:2 A14 M_A2:5

DM2 S_CK3 A13 M_CK3

DM1 S_E3:5 A12/BC# M_A2:4

DM0 S_E2:6 A11 M_A2:6

Control

2

CKE1 M_A3:2 A10/AP M_C1:3

CKE0 M_A3:1 A9 M_A2:1

S3# S2_C2:5 A8 M_A2:0

S2# S2_C3:0 A7 M_A2:3

S1# M_C3:4 A6 M_C0:2

S0# M_C3:3 A5 M_A2:2

BA2 M_A3:0 A4 M_C0:5

BA1 M_C3:7 A3 M_C1:0

BA0 M_C1:6 A2 M_Q1

A15

M_CK0 A1 M_C1:1

A14 M_A2:5 A0 M_C1:5

A13 M_CK3 Orphans PAR_IN M_C1:2

A12/BC# M_A2:4 ERR_OUT# M_A2:7

A10/AP M_C1:3 TEST M_A3:7

RAS# M_C3:6 RESET# M_A3:6

CAS# M_C3:5 ODT1 M_C3:1

WE# M_C1:7 ODT0 M_C3:2

Misc

2,5

MISC1 M_A3:5

MISC0 M_A3:4

DDRCK0 M_C1:4

Table 5 – B_DDR3D_3A (<=1333MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. These signals are required for accurate acquisition and post-processing of acquired data

3. The ‘S’ in front of a TLA channel denotes the Slave card of the merged pair

4. The ‘M’ in front of a TLA channel denotes the Master card of the merged pair

5. MISC1 and MISC0 are placeholders only and will not have interesting data on them