DDR3THIN-MN-XXX 70 Doc. Rev. 1.11

Symbol Definition

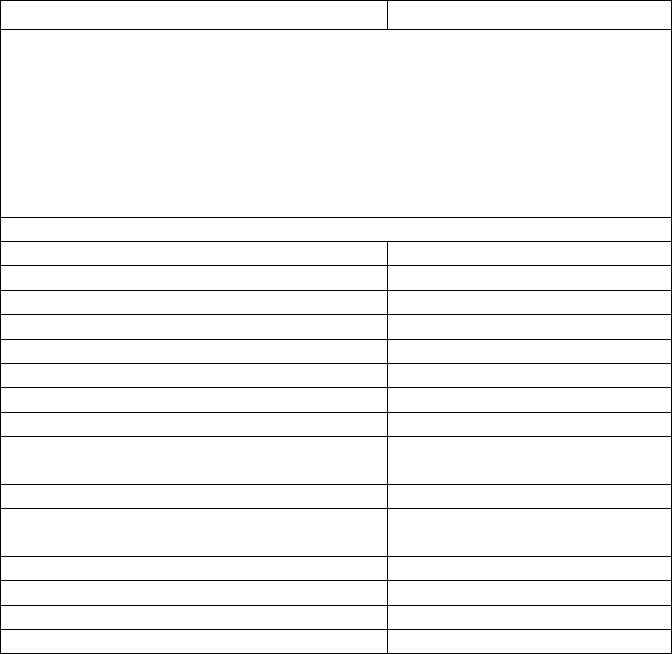

cccc ssssssss = xxxxx1 1110 for S0#

cccc ssssssss = xxxx1x 1101 for S1#

cccc ssssssss = xxxxx1 1011 for S2#

cccc ssssssss = xxxx1x 0111 for S3#

cccc ssssssss = xxxxx1 1110 for bS0#

cccc ssssssss = xxxx1x 1101 for bS1#

cccc ssssssss = xxxxx1 1011 for cS0#

cccc ssssssss = xxxx1x 0111 for cS1#

x in Definition = Don’t Care

MRS – Sx# MODE REGISTER SET cccc ssssssss xxx xxx xx000

MRS – bSx# MODE REGISTER SET cccc ssssssss xxx xxx xx000

MRS – cSx# MODE REGISTER SET cccc ssssssss xxx xxx xx000

REF – Sx# REFRESH cccc ssssssss xxx xxx xx001

PRE – Sx# SINGLE BANK PRECHARGE cccc ssssssss xxx xxx x0010

PREA – Sx# PRECHARGE ALL BANKS cccc ssssssss xxx xxx x1010

ACT – Sx# ACTIVATE BANK cccc ssssssss xxx xxx xx011

WR – Sx# WRITE cccc ssssssss xxx xxx x0100

WRA – Sx# WRITE WITH AUTO

PRECHARGE

cccc ssssssss xxx xxx x1100

RD – Sx# READ cccc ssssssss xxx xxx x0101

RDA – Sx# READ WITH AUTO

PRECHARGE

cccc ssssssss xxx xxx x1101

NOP –Sx# NO OPERATION cccc ssssssss xxx xxx xx111

DES - DEVICE DESELECT cccc ssssssss xxx xxx xxxxx

ZQCL – Sx# ZQ CALIBRATION LONG cccc ssssssss xxx xxx x1110

ZQCS – Sx# ZQ CALIBRATION SHORT cccc ssssssss xxx xxx x0110

Table 9 - B_DDR3D_2G Control Symbol Table

Signals, left-to-right: cCKE1, cCKE0, bCKE1, bCKE0, CKE1, CKE0,

cS1#, cS0#, bS1#, bS0#, S3#, S2#, S1#, S0#,

BA2, BA1, BA0, A15, A14, A13, A12/BC#, A10/AP, RAS#, CAS#, WE#

7.3 Capturing MRS (Mode Register Set) Cycles

If the characteristics of the DDR target (latency, burst length) are not known it is possible to

acquire this information using the TLA so that the post-processing Control settings can be

properly set. This information is programmed into the DDR memory upon system boot by use of

the MRS (Mode Register Set) command, and is required when using the NEX-DDR3INTR-

THIN supports for the post-processing software to properly decode the acquisitions. The TLA

trigger shown in Figure 19 can be used to acquire the MRS cycles when using either of these

supports.

Note that because there is no Trigger event defined in this example that it will be necessary to

Stop the TLA acquisition manually to display the MRS data. A trigger could certainly be added

in either (or both) of the Trigger events, but the method shown ensures that the last valid MRS

cycles will be acquired regardless of the memory depth setting of the acquisition card.